### CS304PC: COMPUTER ORGANIZATION AND ARCHITECTURE

| B.TECH II Year I Sem. | L | Т | Ρ | С |

|-----------------------|---|---|---|---|

|                       | 3 | 0 | 0 | 3 |

Co-requisite: A Course on "Digital Logic Design and Microprocessors".

#### Course Objectives:

- The purpose of the course is to introduce principles of computer organization and the basic architectural concepts.

- It begins with basic organization, design, and programming of a simple digital computer and introduces simple register transfer language to specify various computer operations.

- Topics include computer arithmetic, instruction set design, microprogrammed control unit, pipelining and vector processing, memory organization and I/O systems, and multiprocessors

#### Course Outcomes:

- Understand the basics of instructions sets and their impact on processor design.

- Demonstrate an understanding of the design of the functional units of a digital computer system.

- Evaluate cost performance and design trade-offs in designing and constructing a computer processor including memory.

- Design a pipeline for consistent execution of instructions with minimum hazards.

- Recognize and manipulate representations of numbers stored in digital computers

### UNIT - I

Digital Computers: Introduction, Block diagram of Digital Computer, Definition of Computer Organization, Computer Design and Computer Architecture.

Register Transfer Language and Micro operations: Register Transfer language, Register Transfer, Bus and memory transfers, Arithmetic Micro operations, logic micro operations, shift micro operations, Arithmetic logic shift unit.

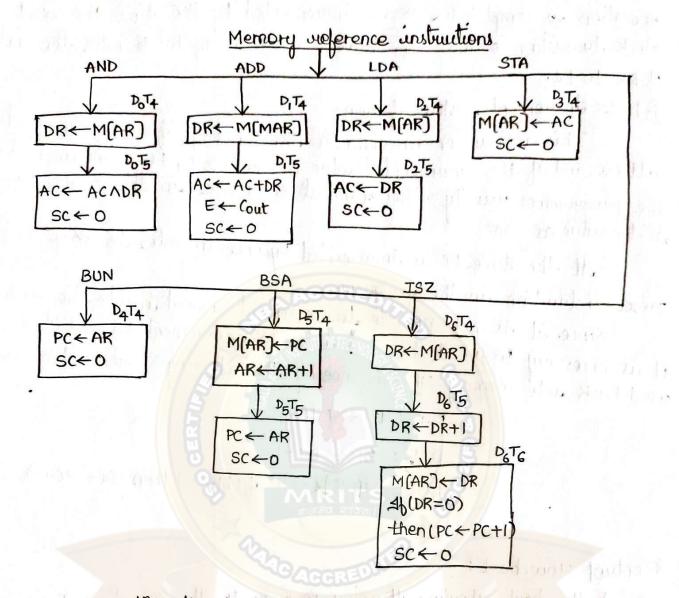

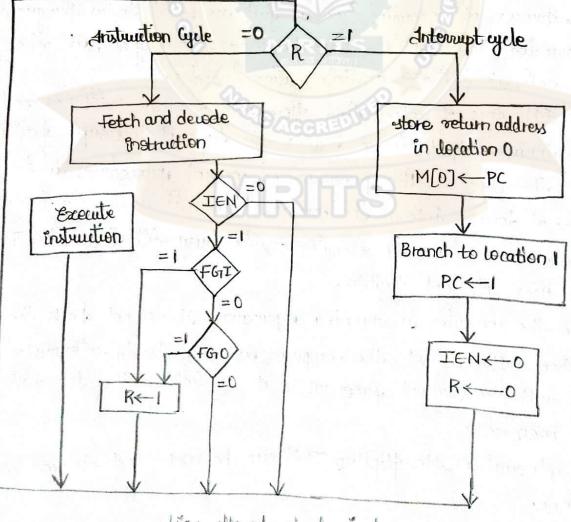

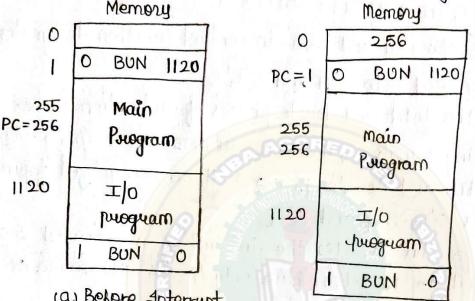

Basic Computer Organization and Design: Instruction codes, Computer Registers Computer instructions, Timing and Control, Instruction cycle, Memory Reference Instructions, Input – Output and Interrupt.

### UNIT - II

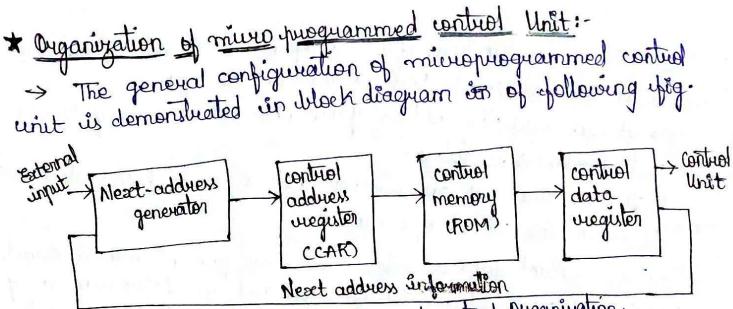

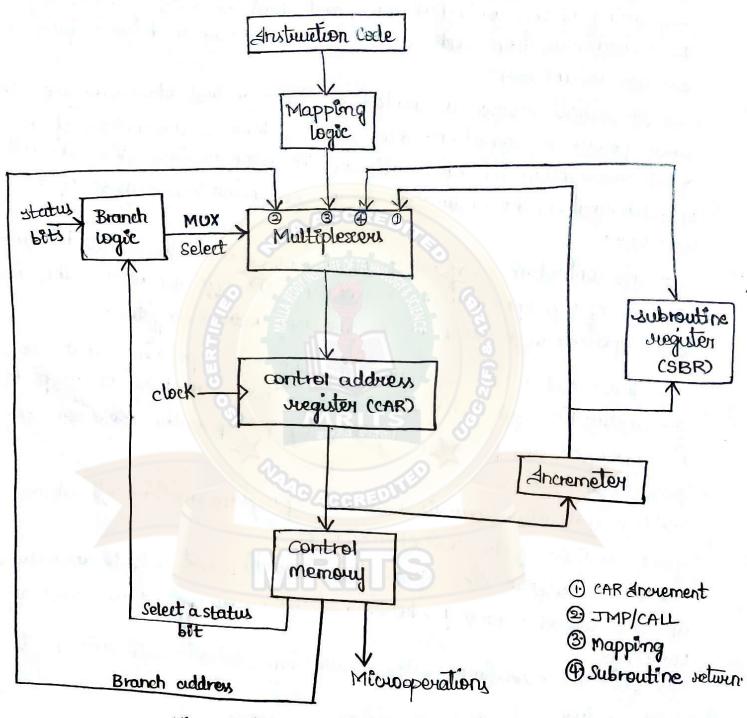

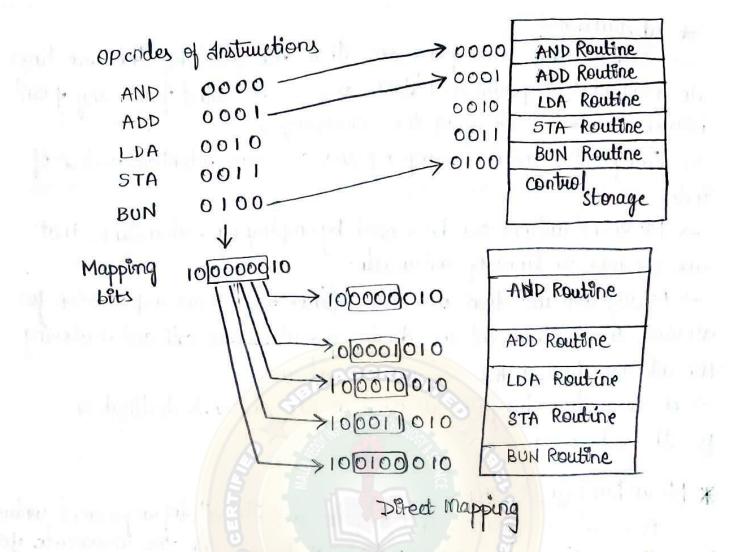

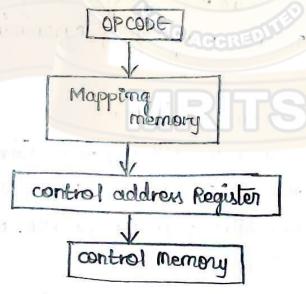

Microprogrammed Control: Control memory, Address sequencing, micro program example, design of control unit.

**Central Processing Unit:** General Register Organization, Instruction Formats, Addressing modes, Data Transfer and Manipulation, Program Control.

### UNIT - III

**Data Representation:** Data types, Complements, Fixed Point Representation, Floating Point Representation.

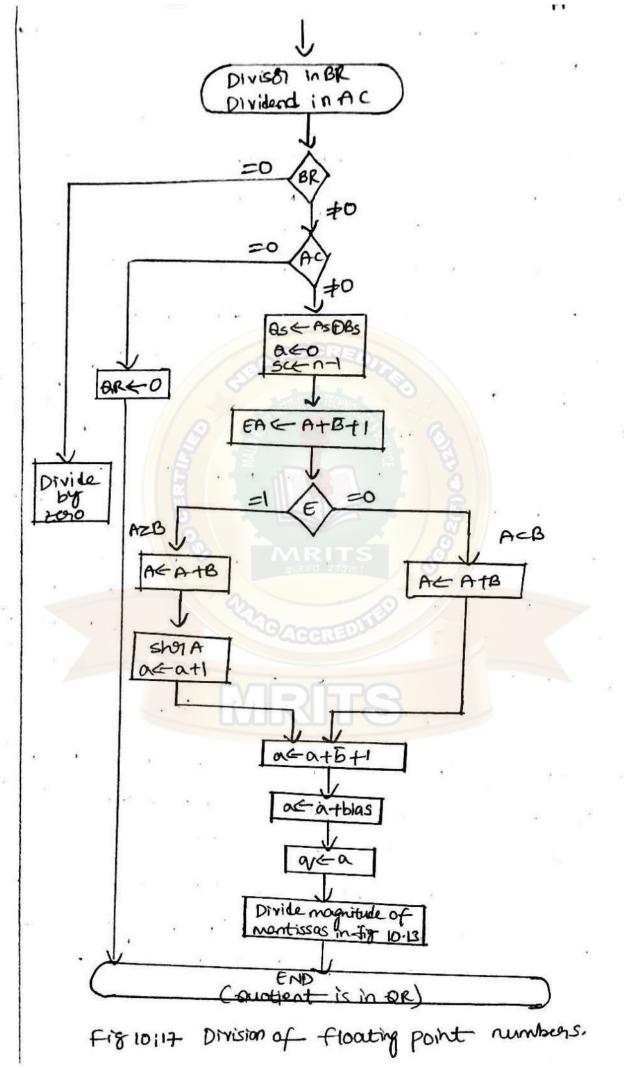

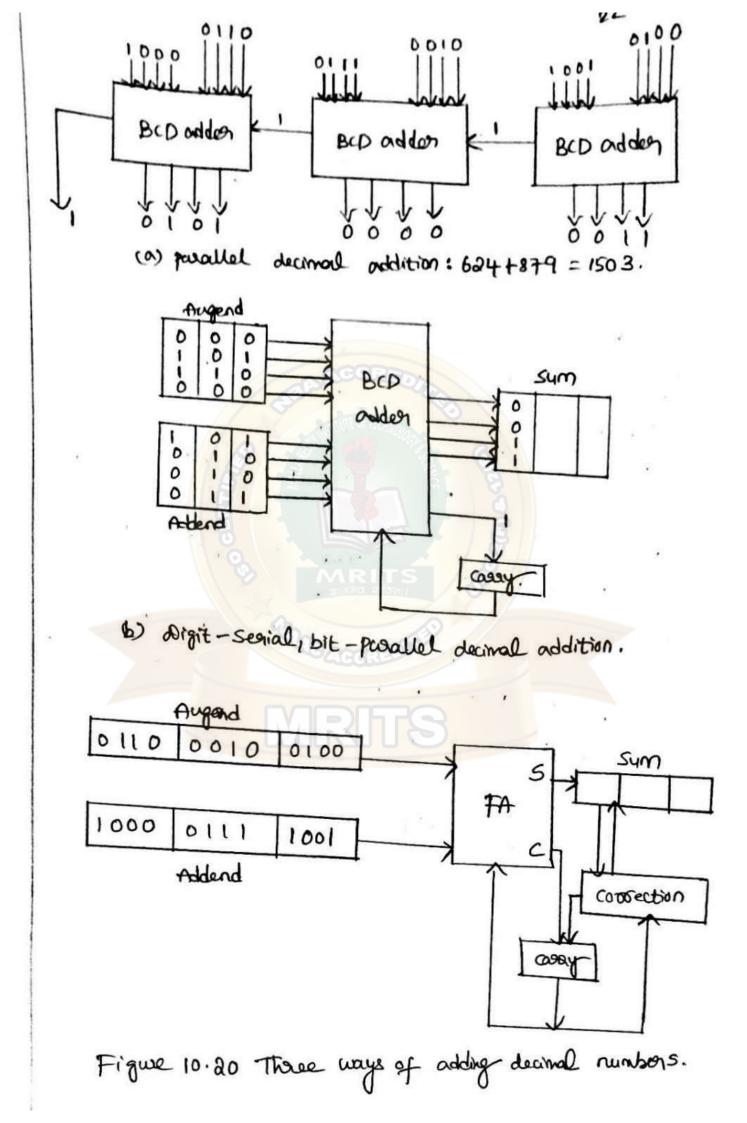

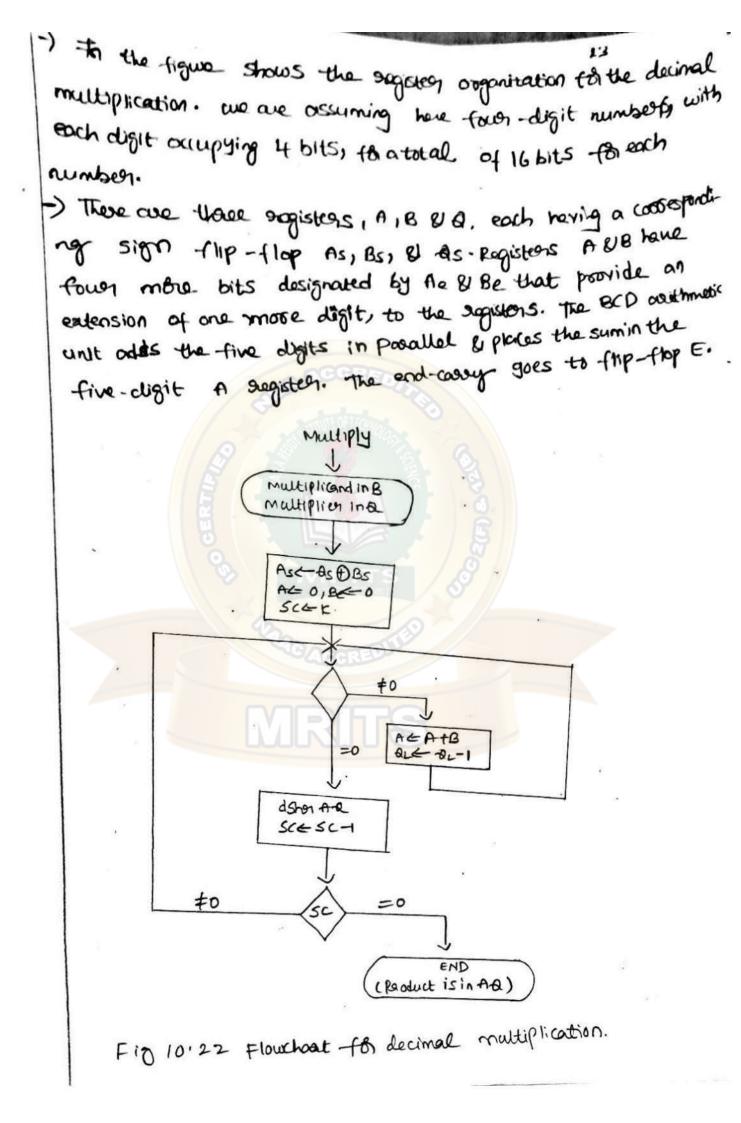

**Computer Arithmetic:** Addition and subtraction, multiplication Algorithms, Division Algorithms, Floating – point Arithmetic operations. Decimal Arithmetic unit, Decimal Arithmetic operations.

### UNIT - IV

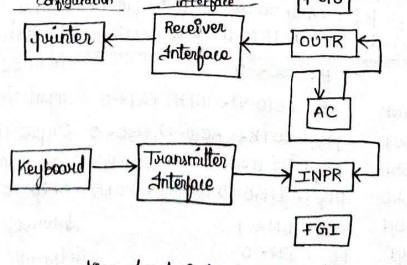

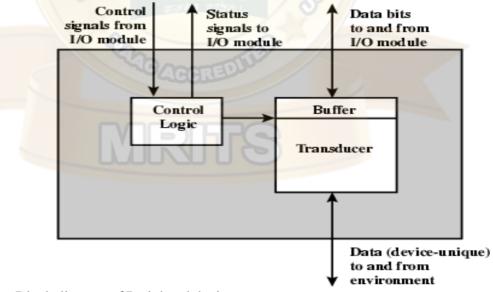

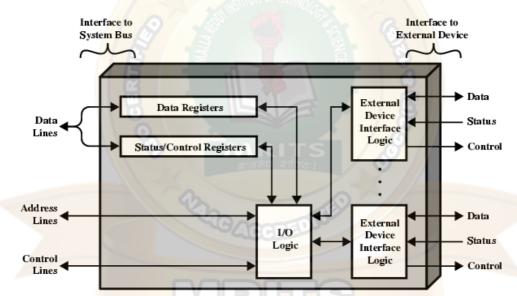

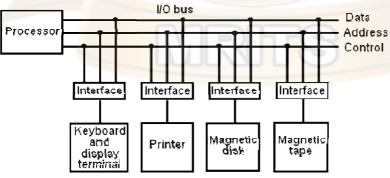

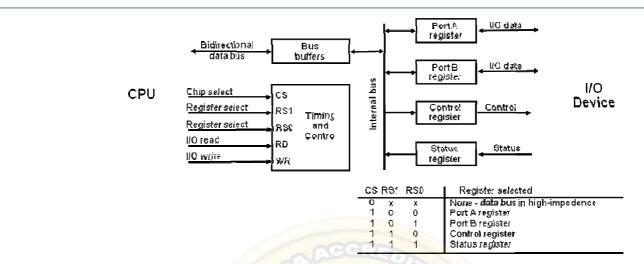

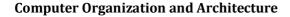

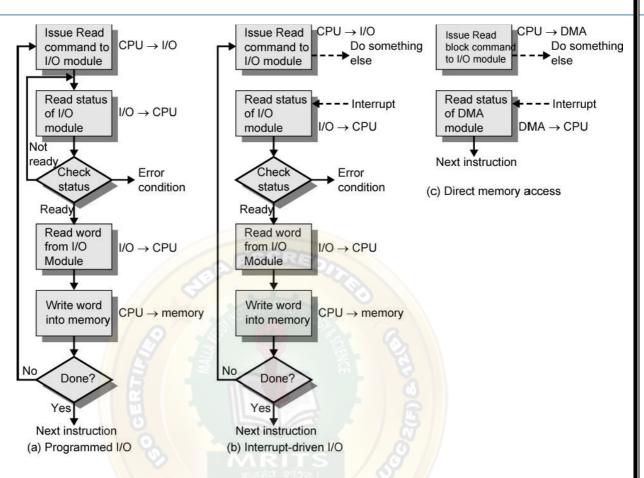

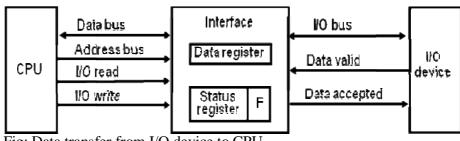

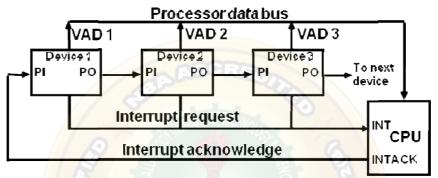

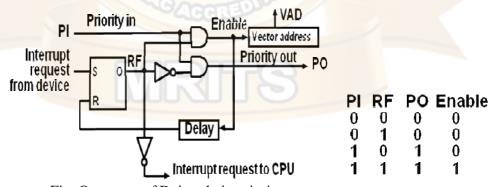

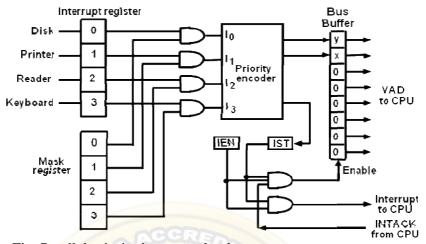

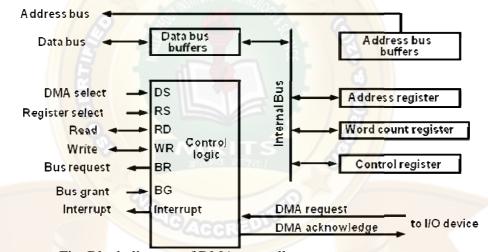

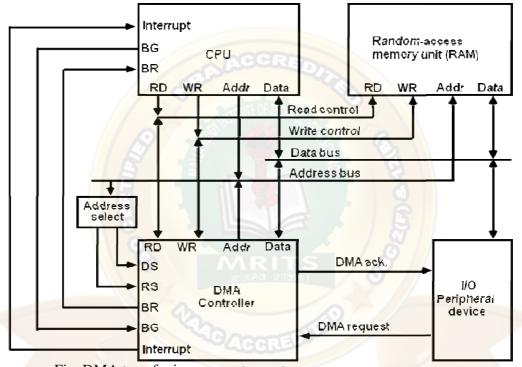

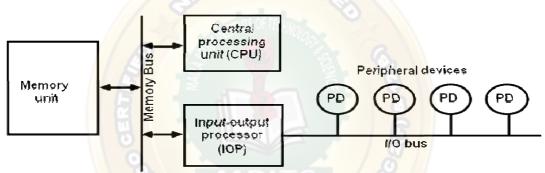

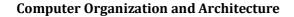

**Input-Output Organization:** Input-Output Interface, Asynchronous data transfer, Modes of Transfer, Priority Interrupt Direct memory Access.

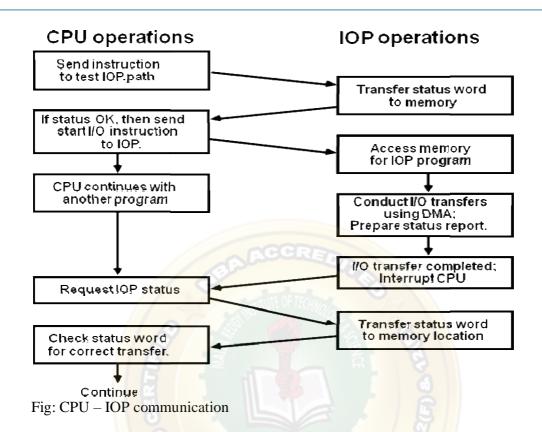

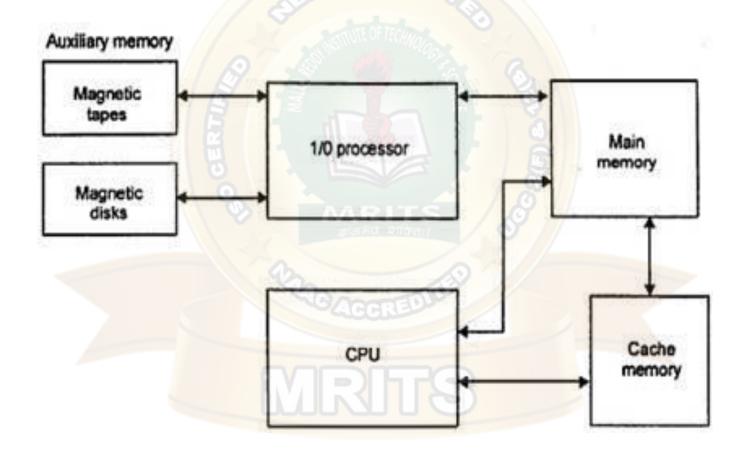

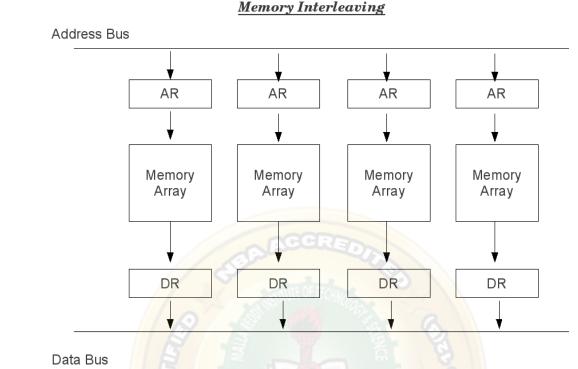

Memory Organization: Memory Hierarchy, Main Memory, Auxiliary memory, Associate Memory, Cache Memory.

### UNIT - V

Reduced Instruction Set Computer: CISC Characteristics, RISC Characteristics.

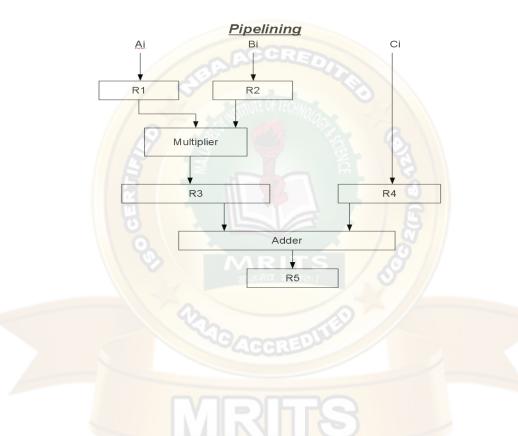

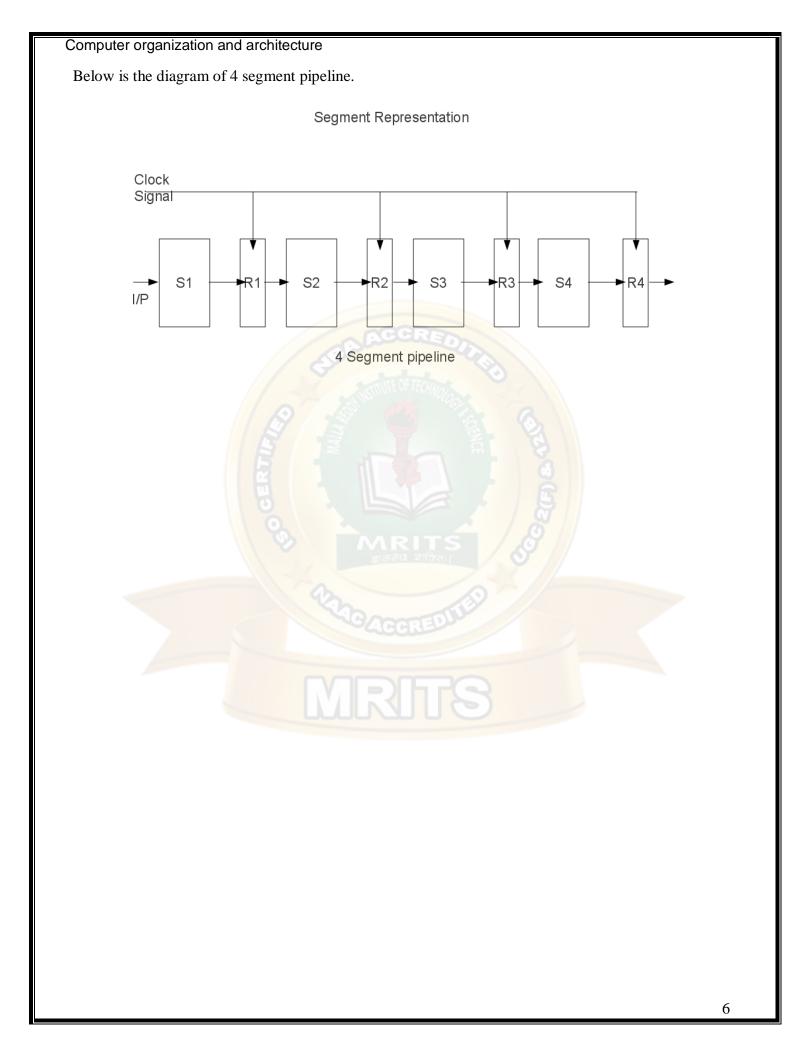

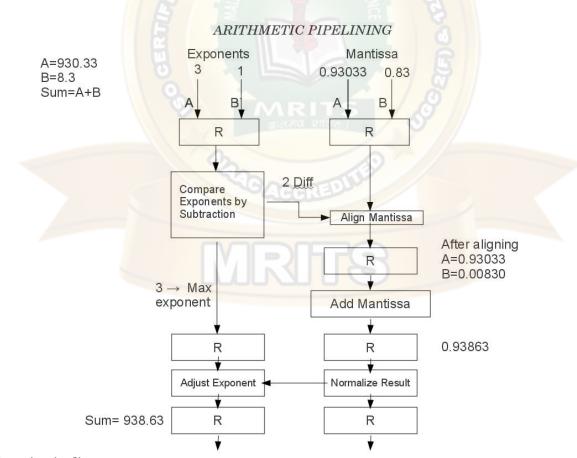

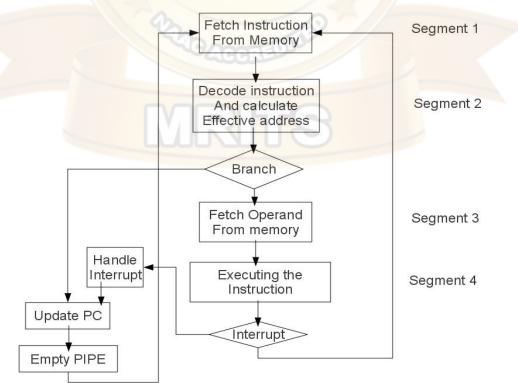

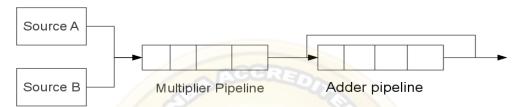

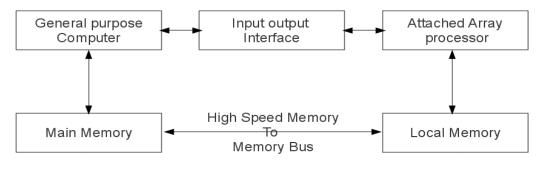

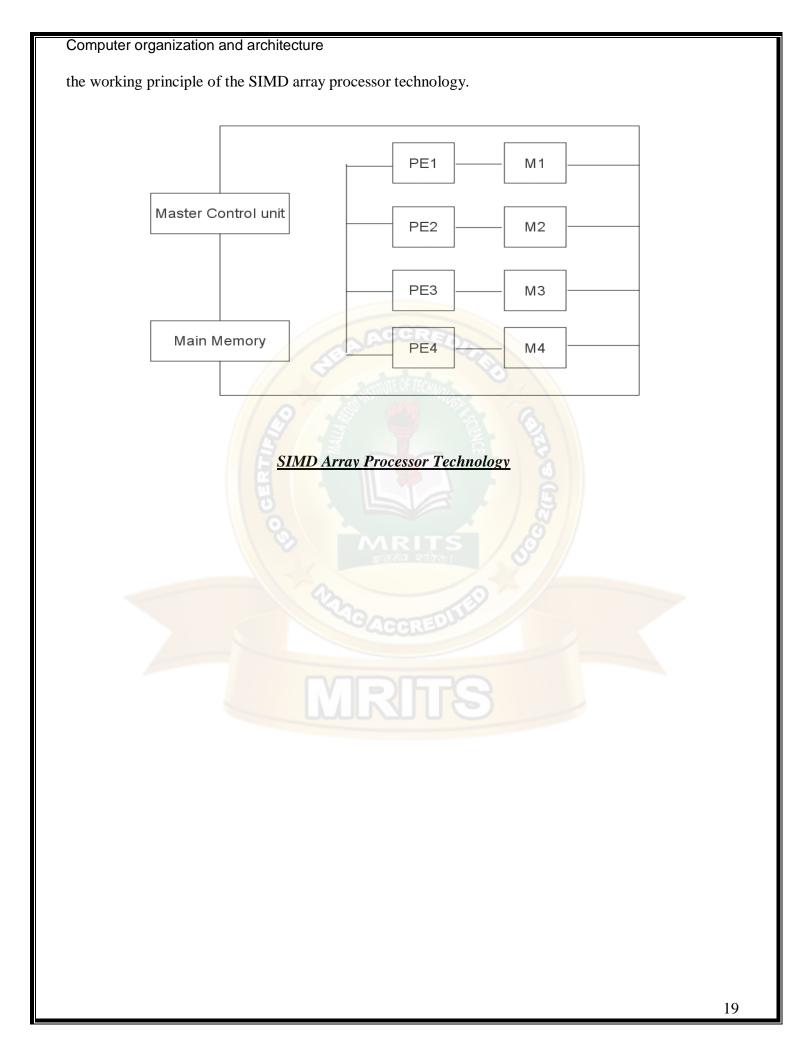

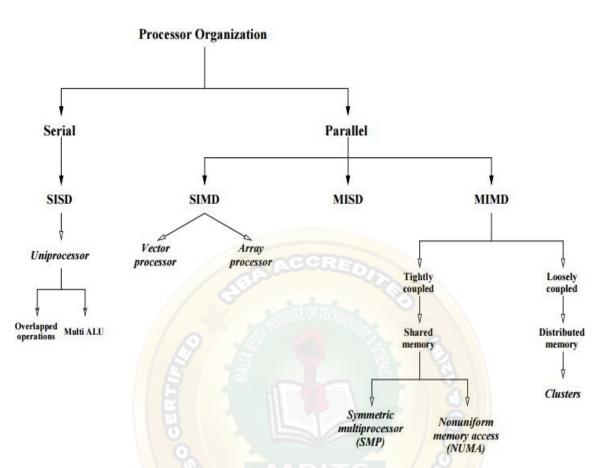

**Pipeline and Vector Processing:** Parallel Processing, Pipelining, Arithmetic Pipeline, Instruction Pipeline, RISC Pipeline, Vector Processing, Array Processor.

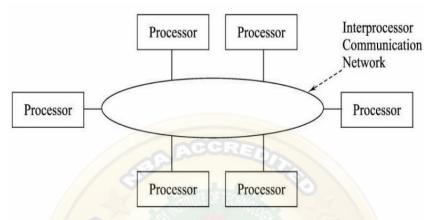

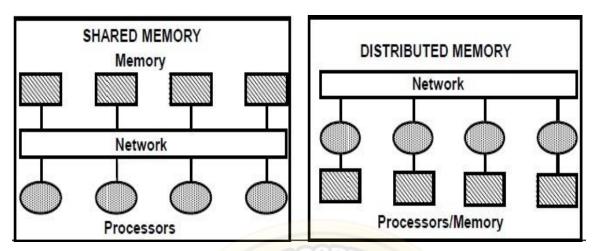

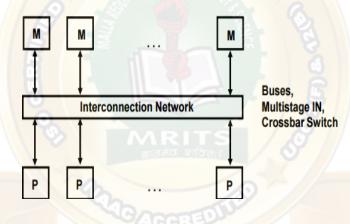

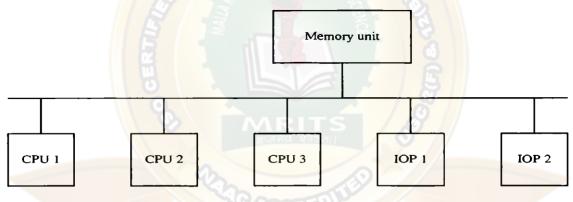

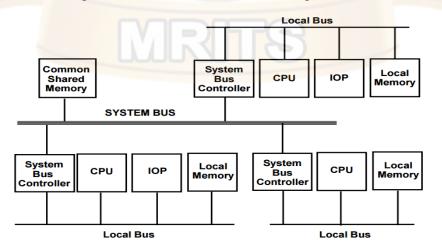

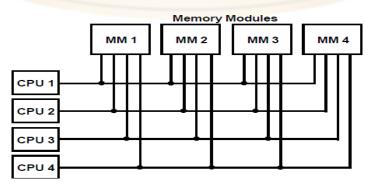

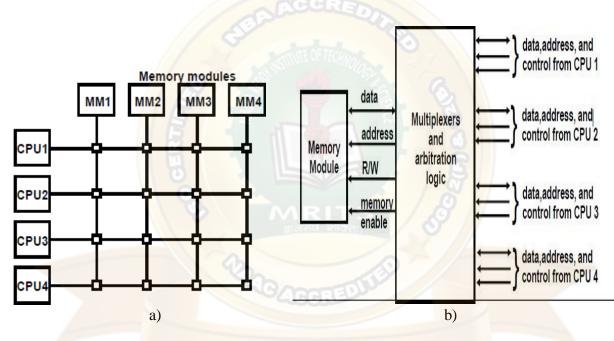

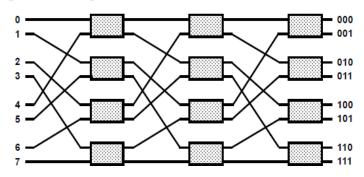

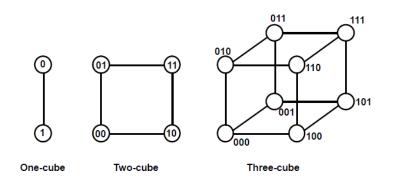

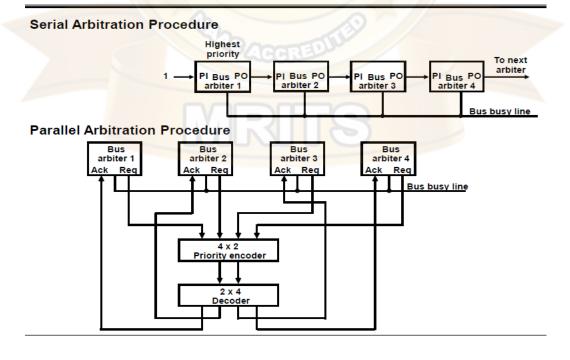

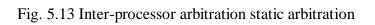

**Multi Processors:** Characteristics of Multiprocessors, Interconnection Structures, Interprocessor arbitration, Interprocessor communication and synchronization, Cache Coherence.

### TEXT BOOK:

1. Computer System Architecture - M. Moris Mano, Third Edition, Pearson/PHI.

### **REFERENCE BOOKS:**

- 1. Computer Organization Car Hamacher, Zvonks Vranesic, Safea Zaky, V<sup>th</sup> Edition, McGraw Hill.

- 2. Computer Organization and Architecture William Stallings Sixth Edition, Pearson/PHI.

- 3. Structured Computer Organization Andrew S. Tanenbaum, 4<sup>th</sup> Edition, PHI/Pearson.

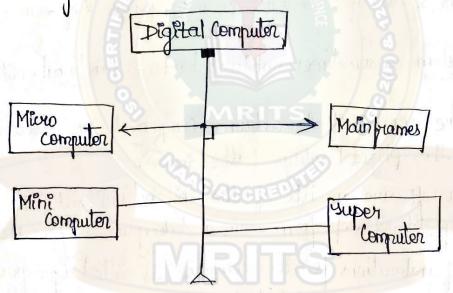

Digotal Computer :-Antroduction :-

At is the most commonly used type of Computer and is used to process information with quantities using digits, usually using the binary number system.

\* Digital Computers are programmable machines that use Electronic technology to generate, store and process data

\* Digital Computers use the binary number system which has 2 digits Oand 1. of winawy digit is called a bit.

\* The two terms positive "1" and nonpositive "o", compose the data into a string.

→ Micuo Computer :-

1/4+ is a small, relatively inexpensive computer with a microprocessor as its CpU. At includes a micropriocessor, memory and 5/0 devices.

4 Also known as "previsional computer"

4 Ancludes woorkstations, desktops, server, laptop & notebook.

→ Mini Computer:-

5 Mini computers emerged in the mid-1960s and were first developed by SBM Corporati -ton.

4 This may also be called a mid-range computer.

4 Minicomputer may contain 104 more processors, support multiprocessing & tasking.

→ Mainframes Computer:-4 Main frames are a type of computer that generally are Known for their large size, amount of Storage, processing power and high level of reliabelity. 4-Ability to run (or host) multiple operating systems. 4 Mainframes first appeared in early 1970s. → Super Computer:-L'Super computer consists of tens of thousands of prioressors that are able to perform bellions & trellions of calculations or computations per second. > These are primarily designed to be used in enterprises and organizations that viequire massive computing power. 4 thas more than 98,000 processors that allows it to process at a spreed of 16,000 Tullion calculations per second. 4 is a darge & very powerful moin frame computer called Supercomputer. 4 Super computers are applied to the solution of very complex & sophisticated scientific quoblem & used for national security purposes of some advance nations. \* d'Computer System is sometimes subdivided into 2 junctional entities : Hardware & software L'Hardware consists of all Electronic components and electromechanical devices that comprise the physical entity of the device. 4 computer Software consists of the instructions and data that the computer manipulates to perform various data processing tasks. \* A sequence of instructions for the computer is called a program." \* The data that are manipulated by the program constitute the data base.

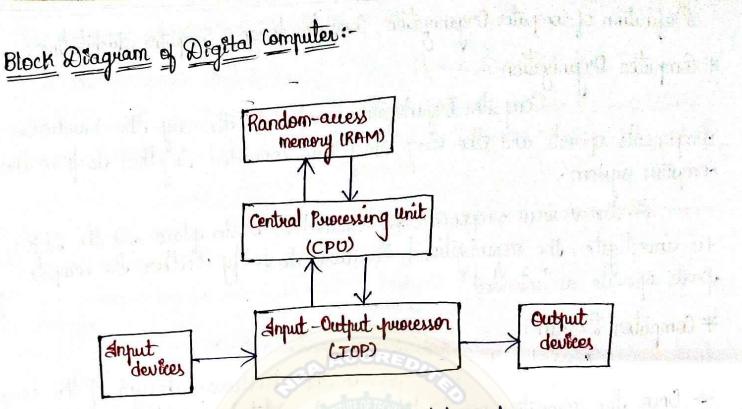

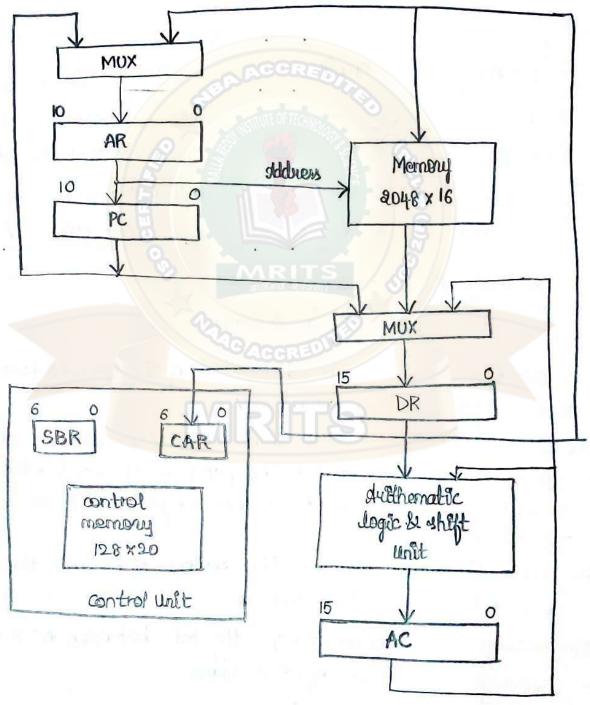

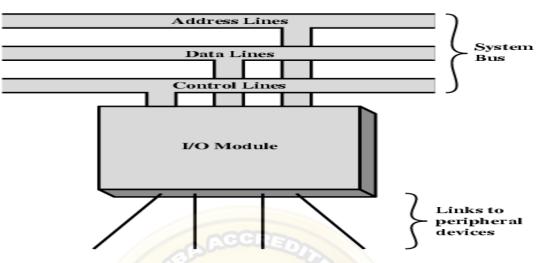

fig: Block diagram of Digital Computer

\* The central processing unit (CPU) contains an arithematic and logic unit for data manipulating data, a number of oregisters for storing data and control counits for fetching and excerting instructions.

\* The memory of a digital computer contains storage for instructions and data At is called as Random datess memory (RAM) because the CPU can access any location in memory at vandom & can vietnieve the binary information within a fixed interval of time.

\* Angut and Output processor (IOP) contains electronic circuits for communicating and controlling the transfer of unformation 5/10 the computer and the outside sould.

\* The Anjuit devices are used by the computer to take input from a user. Eg: Mouse, Keyboood, scanner etc;

\* The Output devees are used by the computer to give Output to the user. Eg:-Printer, Moniter, speaker etc;

Computer Organization vielers to the way the hardware components operate and the way they are connected together to form the computer system.

As the various components are assumed to be in place and the task is to investigate the organizational structure to verify whether the computer parts operate as intended.

Set County - The Partie S.

\* Computer Design :-

Computer design refers to the hardware design of the computer → Once the computer specifications are formulated it is the task of the designer to develop hardware for the system. → The term Computer design is concerned with the determination of what hardware should be used and how parts should be connected. → As the word computer hardware can be referred to as computer implementation.

\* Computer Architecture :-

computer dupitecture refers to the structure and behavior of the computer as seen by the user. At inellides the information, formats, instruction set, and techniques for addressing memory.

The architectural design of a computer system is concerned with the specifications of various functional modules such as processors and memories & structuring them together into a computer system.

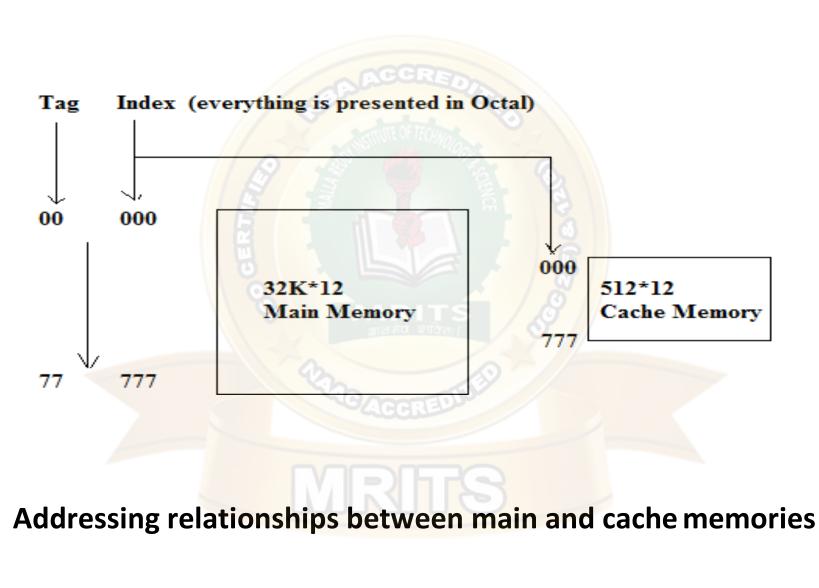

There are two basic types of computer architectures are von Neumann architecture and Hanvard architecture

Von Neumann & Haward Architecture

### Von-Neumann duchitecture

>At is ancient computer architecture based on stored program computer concept

-> Same physical memory address is used for instructions & data.

-> There is common bus for data & instruc -thor transfer.

> Two clock cycles are required to execute Ingle instruction

→ at is cheaper in cost

-> CPU can not access unstructions and read/write at the same time.

> At is used in personal computers and small computers

differences ()

Howard duchitecture

-> At is modern computer cuchitecture based on Houward mark S relay based model

-> Seperate physical memory address is used for instructions & data,

→ Seperate truses are used for transferring data & instruction.

-> de instruction is executed in a single cycle.

> at is costly than Von Neumann architecture.

-> CPU can access instructions and read/write at the same line

→ It is used in microcontrollers & signal processing

Difference between computer Organization and computer duchitecture :-Computer Organization Computer duchitecture.

-> computer Organization is concerned with the way hardware components are connected together to your a computer system.

> At deals with the components of a connection > At acts as interface b/w hardware & software in a system.

→ At tells us how exactly all the units in → At helps us to understand the junctionalities the system are avanged and interconnected. of a system.

→ At converses the realization of architer > d programmer can view architecture inter-tive

-ture

-> In organization is done on the basis of architecture

-> At deals with Low-level design issues -> computer Organization involves ephysical components (circuit design, stdders, signals, Perupherals)

-> computer Architecture is concerned with the structure and behaviour of computer system as seen by the user.

→ d'epubquammer can view auchiteiture interm of unstructions, addressing modes & registers. -> vehile designing a computer system auchitectur is considered first > A deals with high-level design usues -> computer Architecture involves logic (Anstruct -ton sets, Addressing modes, Datatypes, Cache optimization).

\* Register Transfer danguage:-→ A digital computer system is an interconnection of digital modules such as registers, decoders, arithematic elements and control logic. -> These digital modules are interionneited with some common data & control paths to form a complete digital system Digital modules are best defined ! by the registers they contain & the operations that are performed on the data stored in them. -> The operations performed on the data stored in registers are called mero-operations. -> I micro-operation is an elementary operation performed on the information stoned in 104 more registers. The result of the operation may replace the prections binary information of a register or may be transferred to another register Examples of microoperations are shift, count, clear & doad. > The Internal havedware organization of a digital system is best defined Ly The set of registers and the flow of data between them. by specefying > The sequence of microoperations performed on the binary information stored 4 The control that initiates the sequence of microoperations. in the registers. \* Register Transfer Language & the symbolic representation of notation used to specefy the sequence of micro-operations. \* An a computer system, data transfer takes place between processon registers and memory and between processor registers & Enput-output systems. These data transfer can be represented by standard notations given below: \* Notations RO, RI, R2 ----, 40 on represent processor registers \* oldvers of memory locations are represented by names such as LOC, # PLACE, MEM etc; \* Annut-Output regiters are represented by names such as DATA IN, DATA out and so on \* The content of register or memory location is denoted by placing square brackets around the name of the register or memory location

\* Register Turansfer :-

→ The term Register transfer viefers to the availability of hardware logic circuits that can perform a given micro operation and transfer the viesult of operation to the same con another register.

→ The information transformed from one register to another register is represented in symbolic form by replacement operator is called Register transfer (Replacement Operator:-

→ In the statement  $R_2 \leftarrow R_1$ , "  $\leftarrow$ " acts as a vieplaiement operator. This statement defines the iterasper of content of viegister  $R_1$  into viegister  $R_2$ ] → The most of the standard notations used for specifying operations on various viegisters are stated below.

⇒ The memory address register is designated by "MAR".

⇒ Pirogram counter "PC" holds the next instruction's address.

⇒ Instruction register "IR" holds the instruction being executed.

> Ry (oprocessor register)

→ The individual flip-flops in an m-bit register are numbered in sequence from 0 through n-1 starting from 0 in the rightmost position & increasing the number toroard the left.

| (a) Register R                    | [76543210]<br>(b) showing individual bits            |

|-----------------------------------|------------------------------------------------------|

| 15<br>R2<br>(c) Numbering of bits | 15 87 0<br>PC(H) PC(L)<br>(d) Divided into two parts |

| fig: Bl                           | eck diagram of viegister .                           |

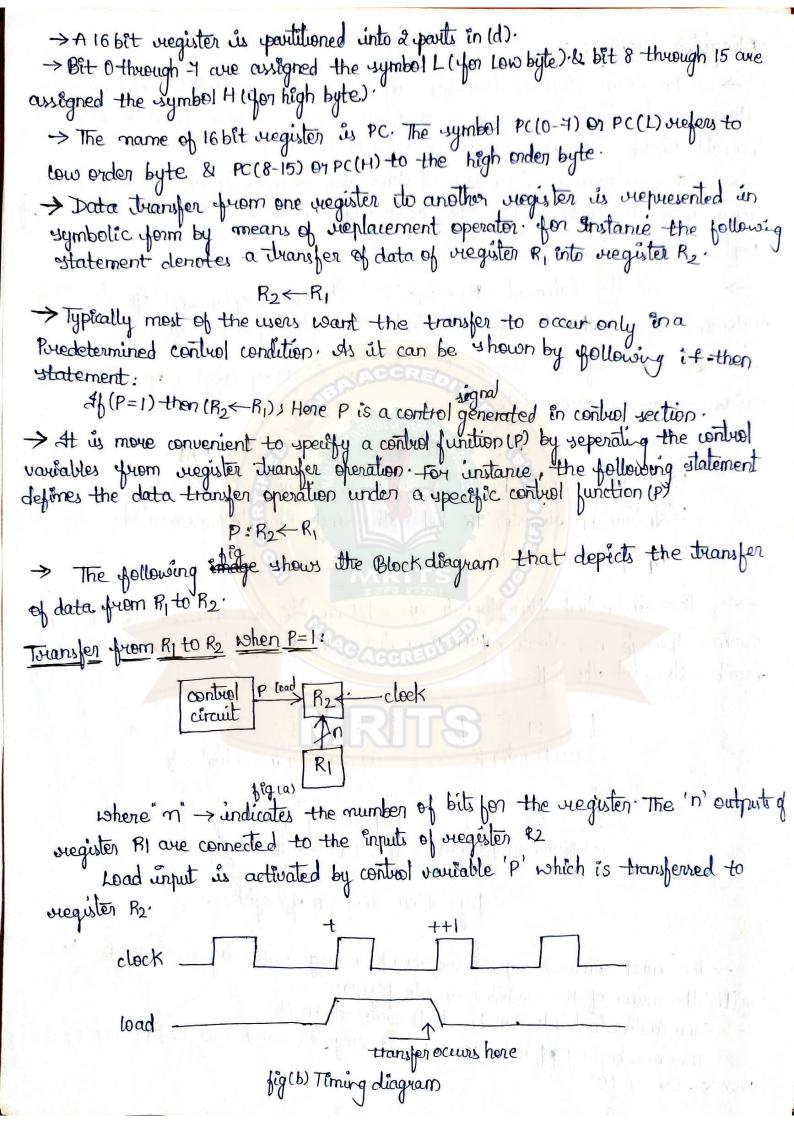

→ The most common way to verviesent a viegister is by a viertangular boxe with the name of the viegister inside fig cas.

-> The Endividual bits can be distinguished in (b)

> The numbering of bits in a 16-bit register can be marked on top of the box shown in (C)

4 An the timing diagram P is activated in control section by the raising edge of clock pulse at time t. 5 The next +ve transition of clock at time t+1 finds the load i/partive & data i/p's of R2 are then loaded into register in parallel.

> P may go back to 0 at time t+1; otherwise, tranfer will occur at every clack pulse transition while P versions active.

The basic symbols of vegister transfer notations are listed in Table O

| Symbol                               | Description                                                      | Examples                                 |

|--------------------------------------|------------------------------------------------------------------|------------------------------------------|

| (1) Letters Capital<br>(and numerals | Denote a register                                                | MAR, R2                                  |

| (and numerals                        |                                                                  | R2(0-7), R2(L)                           |

| (2) Parentheses ()                   | Denotes a pent of a g                                            | $R_2 \leftarrow R_1$                     |

| 3) Annowster                         | Denotes transfer of Enformation                                  | $R_2 \leftarrow R_1, R_1 \leftarrow R_2$ |

| (4) Comma,                           | reperates two microoperations<br>Lermenation of control junction | $P:R_2 \leftarrow R_1$                   |

|                                      | Leaning of the p                                                 | if P=1                                   |

### \* BUS AND MEMORY TRANSFERS:-

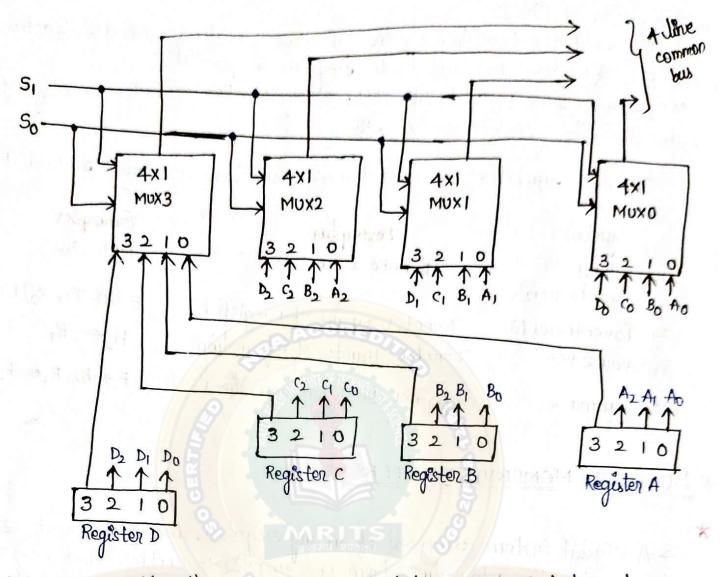

→ A digital system composed of many registers, and paths must be quourded to transfer information from one suggister to another. The no. of wires will be excessive if separate lines are used between each register and all other register in the system. → A bus structure, on the other hand, is more efficient for transferring information between registers in a multi-register configuration system. > A bus consists of a set of common lines, one ofor each bit of register determine which beinaw information is transferred one at a time. Control register determine which register is selected by the bus during a sparilicular suggister transfer. > One way of constructing a common bus system is with multiplezers. The following block diagram shows a bus system for 4 registers. At is constructed with the help of for 4×1 Multiplezers each having four data ip's (0 to 3) & selection ipputs (S1 and S2).

> For instance output 1 of register A is connected to input 0 of MUX1

Bus isystem for 4 registers :-

-> The itwo selection lines S, & So are connected to the selected inputs of all 4 multiplexers.

-> The selection lines choose the four lits of 1 register & transfer them into the

> when both of the select lines are at low logic, i.e., S,So=00, the 0 data i/ps of all four multiplezers are selected and applied to the 0/p's that forms the bus This in two, causes the bus lines to receive the content of register A strice the output of this register are connected to the data o i/ps of the multiplezers > stratarly, when S1So=01, register B is selected, and the bus lines will receive the content provided by register B.

> The following function table shows the negister that is relected by the buy for each of the 4 possible binary values of the selection lines

| SI | S0           | Register<br>Selected |

|----|--------------|----------------------|

| 0  | 0            | A                    |

| 0  | . <b>1</b> . | В                    |

|    | O            | C                    |

|    | 1            | D                    |

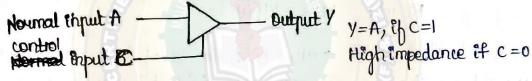

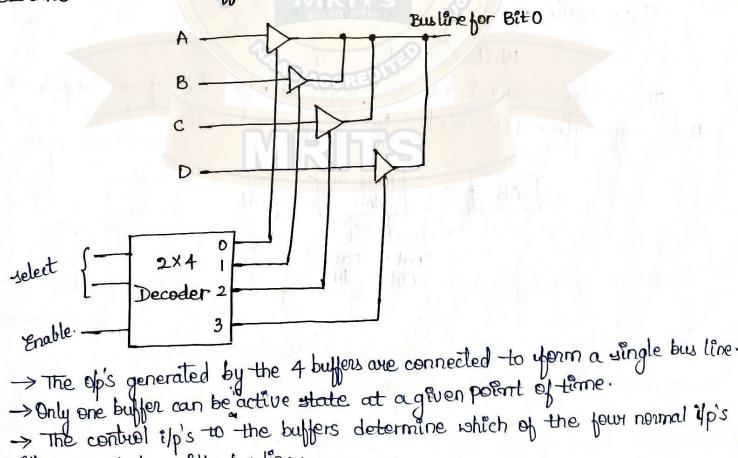

Three state Bus Buffers:--> I dus system an also be constructed using 3 state gates instead of multiplexes -> The three state gates can be considered as a digital circuit that has 3 gates, -> The three state gates can be considered as a digital circuit that has 3 gates, -> The three state gates can be considered as a digital circuit that has 3 gates, -> The three state gates can be considered as a digital circuit that has 3 gates, -> The three state gates can be considered as a digital circuit that has 3 gates, -> The state gate exclusion to degic 1 and 0 as in a conventional gate. Now ever, the 3<sup>rd</sup> gate exclusions a state gates in case of the bus system is a. -> The most commonly used three state gates in case of the bus system is a. buffer gate. The graphical symbol of a three state buffer gate and be represented as

Bus line with 3 state buffer:-

will communicate with bus line.

→ A 2×4 decoder ensures that no more than one control ip is active at any given point of time.

W parameter 1

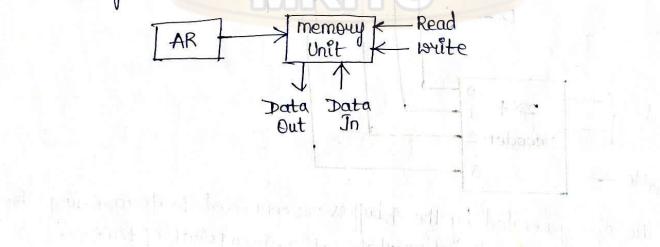

\* Memory Wansfer:-

Most of the standord notations used for specifying operations on memory transfer are stated below.

> The transfer of information from a memory unit to the enduser is called Read eperation .

> The triansfer of new information to be stored in the memory is called inte oriention voute operation

A memory word is désignated by letter M.

At is necessary to specify the address of "M" when writing memory transfer operations. This will be done by enclosing the address in square brackets yollowing the letter M.

The address register is designated by AR and the data register by DR. Thus a read operation can be stated as

A A Bloand

Read:  $DR \leftarrow M[AR]$

The read statement causes a transfer of information into the data register (DR) from the memory word (M) selected by address register (AR). 拉方 (1) 9(1) 451

The write operation can be stated as

Wrfte:  $M[AR] \leftarrow R_1$

The write statement causes transfer of information from register R, into the memory word (M) selected by address register (AR

an and in the standing to the optimized of the stands with the standing of the standing of the standing of the

and the shall be the start of the

a state of the second stat

Mius operations :-

d microoperation is an elementary operation performed with the data stored in vegisters. An digital computers, microoperations are classified into your categories :

• Register transfer micropperations transfer trinary information from one

register to another. @ stat duithematic microoperations perform withematic operation on

numeric data stored in registers 3 Logic microoperations perform bit manipulation eperations on non

-numeric data stored in registers. (4) Shift microoperations porform shift operations on data stored in

registers.

### \* drithematic nicrooperations:-

shuthematic microoperations deals with the operation performed on numeric data stored in the registers. The basic arithematic microoperation are classified as follows

- is shift 4 dditten

- 4 subtraction

- 5 Inviement

- 13 decrement.

some additional arithematic microoperations are

is sidd with carvy

y subtract with borrow

13 Transfer/Load, etc.,

The following table shows the symbolic representation of Arithematic mero operations

| -symbolic designation           | Description                                      |

|---------------------------------|--------------------------------------------------|

| $R_3 \leftarrow R_1 + R_2$      | The contents of RI plus R2 -transferred-to<br>R2 |

| $R_3 \leftarrow R_1 - R_2$      | The contents of R1 minus R2 transferred to       |

| $R_2 \leftarrow \overline{R_2}$ | ng<br>Complement the contents of R2.             |

$R_{2} \leftarrow R_{2} + 1$   $R_{3} \leftarrow R_{1} + R_{2} + 1$   $R_{1} \leftarrow R_{1} + 1$   $R_{1} \leftarrow R_{1} - 1$

2's complement the centents of R2 R1 plus the 2's complement of R2 Anciement the contents of R1 by one Decirement the contents of R1 by one.

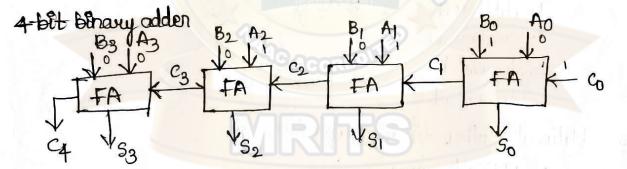

\* Benary Adder:-

> The add microoperation vequires registers that can hold the data and the digital components that can perform anothermatic addition.

→ a binary adder is a digital cirait that performs that the arithematic osum of two binary numbers provided with any length. → A Binary Adder is constructed using full-adder circuits connected in series, with the output carry from one full-adder connected in series, with the output carry from one full-adder

> The block diagram shows the interconnections of your full-adder circuits to provide a 4-bit bloavy adder.

→ The augend bits (A) and addend bits (B) are designated by subscript mumbers your sught to left, with subscript '0' denoting the low order bits'

> The carry T/p's starts from Co to C3 connected in a chain thrue the yull adders. C4 is resultant output carry generated by last F.A.

> The Op carry from each full-adder is connected to the Vp carry of next-high order F.A.

> The sum o/p's (S0 to S3) generates the required arithematic sum of augend & addend bits.

> The m data bits yor the A & B sp's come from different source registers. For Enstance, data bits yor A E/p comes from source register Ry and data bits for B 1/p comes from source register (more) R2. > The arithematic sum of the data ip's of A and B can be transferred to theird register or to one of the registers (R1 on R2)

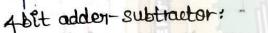

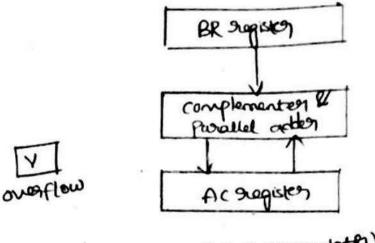

## \* Binary Adder-Subtractor:-

> The subtraction micro operation can be done easily by taking 2's complement of addend bits and adding it to the augend bits > The authematic million operations like addition and subtraction can be combined into one common circuit by including an exclusive-OR gate with each full adder.

> The block diagram for a 4-bit adder-subtractor circuit can be

represented as

-> When the mode input (M) is at a low logic i.e; 'o', the circuit act as an adder & when the mode %p is at high logic, i.e; 1', the

circuit act as a subtractor. > The Exclusive OR gate connected in series succeives i/p M and

→ when Mis at a low logic, we have B⊕0=B. The yull-adders one of i/p B. receive the value of B, the "/p carvy is 0 and the circuit performs

A+B ⇒ when M is at high logic, we have B⊕I=B and CO=1 -> The B ips are complemented and al is added through the ip cavuy. The circuit performs the operation A plus the 2's complement of B.

\* Binary Anciementer :-

→ The invienment mivicoperation adds one binary value ito the value of binary variables stored in a viegister.

> For instance, a 4-bit register has a binary value 0110, when incremented by one-the value becomes 0111.

0110

→ The increment micro operation is best implemented by a 4-bit combinational circuit incrementer. A 4-bit combinational circuit incrementer can be represented by the following block diagram.

→ A logic-1 is applied to one of the inputs of least significant half - adder, and the other ip is connected to the least significant bit of the number to be incremented:

> The output carry from one half-adder is connected to one of the 1/p's of the next higher-order half adder.

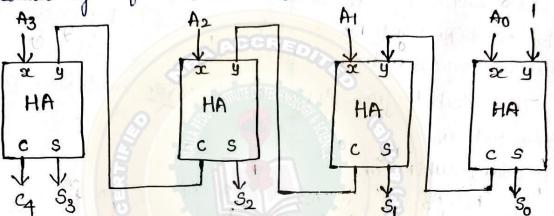

→ The binary invienentar circuit vieceives the four bits from Ao through Az, adds one to it, and generates the invienmented output in So through Sz'

> The output cavery of will be 1 only after incrementing binary 1111-

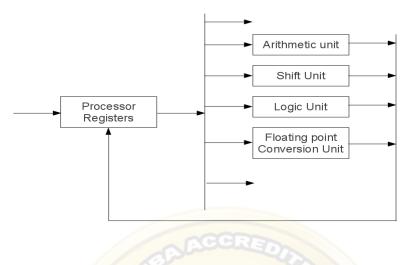

\* Authematic Unit :-

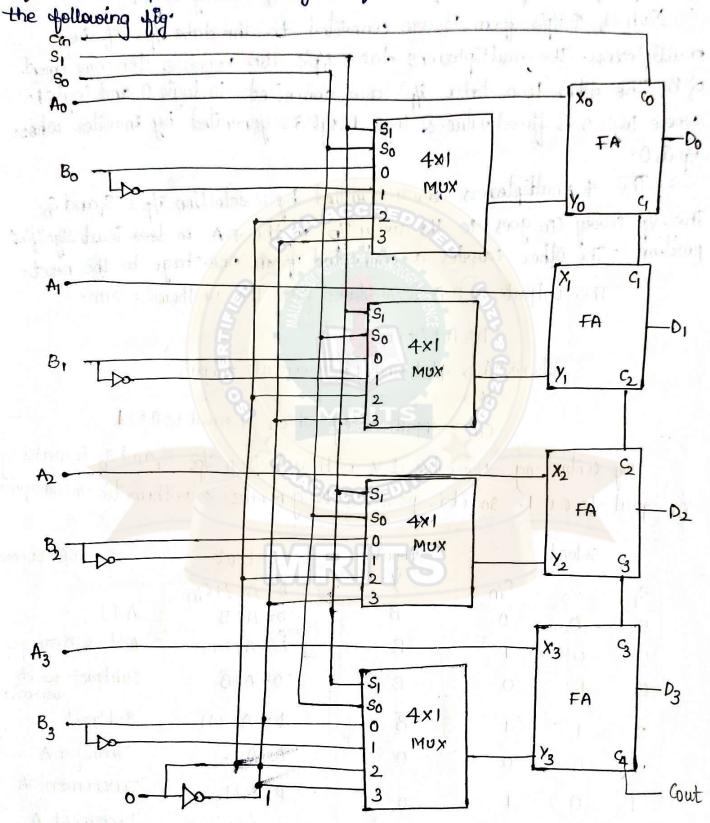

The basic component of an arithematic circuit is parallel adder. By controlling the data i/p's to the adder, it is possible to obtain different types of arithematic operations. The diagram of a 4-bit arithematic circuit is shown in the shellowing the.

112.14

→ The Wock diagram has 4 full adder circuits that constitute the 4 bit adder and your multiplexers for choosing different operations.

→ There are # & 4-bit s/p's A and B and a 4-bit Output D. The your yp's from A go directly to the × 1/p's of binary adder.

→ Each of 4 i/p's from B are connected to the data i/p's of the multiplexers. The multiplexers data 1/p's also receive the complement of B. The other two data i/p's are connected to logic 0 and logic 1.

> The 4 fullipleaers are controlled by & selection 1/p's S, and S. The 1/p cavey (in goes to the cavery 1/p of the FA in test Significat position . The other cavers a connected from one stage to the next. The output of B.A is calculated from the arithematic sum.

$$D = A + Y + Cin$$

where A > 4 bit know numbers at x inputs

Y→ input carry which is equal to D on 1

By controlling the value of y with selection i/ps s, and s & making Cin equal to 0 on 1. so it is possible to generate 8 arithematic microoperation

|                          | Select                          |                         | Anput                      | Output                                                                                                          | meuro operation                          |

|--------------------------|---------------------------------|-------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------|

| S <sub>1</sub><br>0<br>0 | S <sub>0</sub><br>0 -<br>1<br>1 | Cin<br>0<br>1<br>0<br>1 | y<br>B<br>B<br>B<br>B<br>O | $D = A+Y+C_{fr}$ $D = A+B$ $D = A+B+1$ $D = A+\overline{B}$ $D = A+\overline{B}$ $D = A+\overline{B}+1$ $D = A$ |                                          |

| 1<br>1<br>1              | 0<br>1<br>1                     | 1<br>0<br>1             | 0<br> <br>                 | D=A+1<br>D=A-1<br>D=A                                                                                           | Increment A<br>Decrement A<br>Transfer A |

> when S10S0=00 the value B is applied to Y 1/ps of the adder. Addition :-→ af Cin=0 then output D= A+B 1 -then output D= A+B+1 -> An Both cases Add microoperation with on without adding carry are performed. > when SiSo = 01, the complement of B is applied to Y i/p's of the adder. Subtraction :-→ af Cin=1 then 0/p D=A+B+1 (A+ 25 comp of B is equivalent to A-B) O -then O/p D = A+B (This equivalent to subtract with borrow i.e; A-B-1 > when SiSo=10, the ips from B are neglected instead all 0's one inverted into Y i/pis. The olp becomes D=A+0+cin Cin=O then D=A (here direct transfer from ip A to Oup D 1 -then D=A+1 ( the value of A is inversented by 1 > When S, S0= 11, all is are inserted into Y 1/ps of adders to produce the decrement operation D=A-1 when This is because a number with all is equal to 2's complement of 1 (i.e., D=A-1 when Cin=O 2's comp of binary 0001 is 1111) Adding a number A to 2's comp of 1 produces F = A + 2S comp of I = A - I4 when Cin=1 then D= A-1+1=A, which causes a direct transfer from ipA to olp D. .". D=A is generated twice, so there are only 7 clistinct microoperation in -Arithematic circuit. is again a man made an internet the state the part was have o man he appeared to serve the server of the relation of the The equipart A. F. O.I. be used for derete the mathematic arrival

needs of the model of an ender of configuration twenty on the

and which induced in the state of the second of the second second

A DATE AND A

Chealthill had up for and a fast requiries apply

\* Logic microoperations:

Logic microoperations specify binary operations for strings of bits stored in registers. As operations consider each bit of the register seperately and treat them as binary variables.

Eq: - The Exclusive OR microoperation with the contents of two registers R1 and R2 is symbolized by the statement

$P: R_1 \leftarrow R_1 \oplus R_2$

At specifies a logie microoperation to be executed on the

individual bits of registers provided that the control variable P=1.

The Exclusive OR moveoperation stated above symbolizes the following logic computation

1010 -> content of Ri

11 00 → content of R2

0110 -> content of Ry after P=1

The content of R1 after the execution of microoperation, is equal to the bit-by-bit Exclusive OR operation on pairs of bits in R2 & previous values of RI

-> The logic microoperations are widely used in scientific computations, but they are very useful for bit manipulation of binary data & for making logical decisions.

Special Symbols.

special symbols will be adopted for the logic microoperations OR, AND and complement, to distinguish them from corresponding symbols used to express boolean functions.

> The symbol v will be used to denote an OR milurooperation.

-> The symbol A well be used to denote an AND microoperation.

> The complement microoperation is same as 1's complement & uses a bar on top of the symbol that denotes the wegister name.

> By using different symbols, it will be possible to differentiate b/w a logie mérioperation & a control function (Boolean).

→ Anothen viewson for adopting & sets of symbols is to be able to distinguish the symbol+, when used to symbolize an avithematic plus, from a dogic OR operation. → ds + symbol has & meanings, it will be possible to distinguish blw them by nothing where the symbol eccurs. when the symbol + occurs in a microoperation, it will denote an anithematic plus. when it occurs in a control (or boolean) function. It will denote an anithematic plus. When it occurs in a control (or boolean) function. It will denote an or operation. We will mever use it to symbolize an or it will denote an or operation. We will mever use it to symbolize an or

For example,  $P+9: R_1 \leftarrow R_2 + R_3$ ,  $R_4 \leftarrow R_5 \lor R_6$  the + blip P&9 is an OR operation blip two bitnary variables of a control function. The + blip  $R_2 \& R_3$  specifies an add microoperation. The OR microoperation is designated by symbol  $\lor$  blip  $R_5 \& R_5$ List of Legic Microoperations:

There are 16 different legic operations that can be performed with a binary variables. They can be determined from all possible truth tables obtained with two bonary variables as shown in Table below.

| x<br>o     | ч | Fo | -Fi | F2 | F3 | F4 | F5 | F6 | fa | F8 | fq       | -Fio | fn   | fi2   | FI3   | F14     | +15  |

|------------|---|----|-----|----|----|----|----|----|----|----|----------|------|------|-------|-------|---------|------|

|            |   |    |     |    |    |    |    |    |    |    |          |      |      |       |       | 1       | T    |

| 0          |   | -  | 5   | n  | 6  |    |    |    |    | () | <b>U</b> | U    | U    |       |       |         | 1    |

| $< 1^{10}$ | 0 | 0  | 0   | 1  | 1  | 0  | 0  | 1  | I  | 0  | 0        | 0    | 1    | 0     |       | 0       | 1    |

| L          | T | 0  | 1   | 0  | -  | 0  | 24 | 0  | 1  | 0  | SP.      |      | 2 to | Det 1 | Cart. | States. | 1.15 |

An this table, each of 16 columns to to f15 viewesents a T.T of one possible Boolean function for the availables se and y. The functions are determined from 16 binary combinations that can be assigned to f. The 16 boolean functions of a variable se s y are expressed in algebraic form in first column of table 2 and logic microoperations in second column wing ASB viegisty

The 16 logic meuroperations are derived from these functions by replacing & by the binary content of register A & variable y by the binary content of register B.

Each bit of register is treated as a linery variable & the microoperation is performed on the string of bits stored in registers.

| Boolean junction    | Microoperation | Name                 |

|---------------------|----------------|----------------------|

| -Fo=0               | F←0            | clean                |

| -fi=sch             | FEANB          | -And                 |

| -F2= 244            | FLANB          | an Normality         |

| - J<br>F3= 2        | F←A            | Transfor A           |

| f4=22'y             | F~ANB          | parts on spends Ward |

| F5=4                | F←B            | Transfer B           |

| -F6=α⊕y             | F←A⊕B          | Exclusive-OR         |

| •                   | FLAVB          | OR                   |

| Fy=&+y<br>Fg=(x+y)! | F - AVB        | NOR                  |

| V                   |                | Exclusive-NOR        |

| fq = (20By)'        | F← A⊕B         | complement B         |

| -fio= y'            | F + B          | certificate D        |

| fii= x+y'           | FEAVB          | part out the me      |

| $f_{12}=\alpha'$    | FEA            | Complement A         |

| -Fi3=22+4           | F-AVB          | the second states of |

| -Fi4= (xy)'         | F-AAB          | NAND                 |

|                     | Ft all I's     | -set to all is       |

| F15=1               | A mana siba I  |                      |

Hardware Amplementation : The hardware implementation of logic microoperations requires that logic gales be inserted yor each bit or pair of bits in the registers to perform the required logic function.

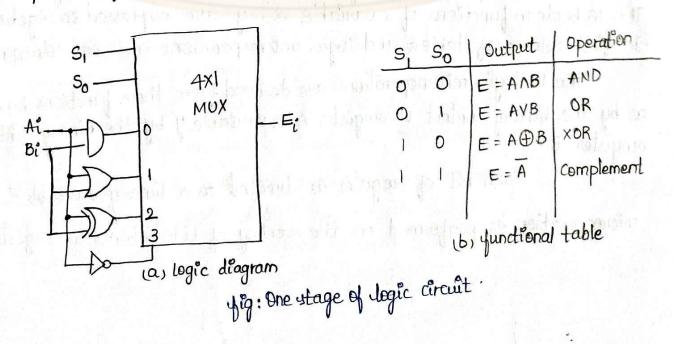

> although there are 16 logic microoperations, most computers use only 4-AND, OR, XOR (Exclusive OR), and complement from which all others can be derived. → Figure shows one stage of a circuit that generates the 4 basic logic microo -perations. At consists of 4 gates & a multiplezer. Each of the 4 logic operations is generated through a gate that performs the required logic.

> The old of the gates are applied to the data ilps of the multiplesser. The two selection ip s, and so choose one of the data ips of multiplezer & direct its value to the olp.

> The diagram shows one typical stage with subscript 1. You a dogic circuit with n bits, the diagram must be repeated n times for i=0,1,2--n-1. > The relection variables are applied to all stages. The function table in Fig-lists the logic microoperations obtained for each combination of selection variables.

$\rightarrow$  Some applications :-

Slogic microoperations are very useful for manipulating individual bits of a portion of word stored in a viegister.

is They can be used to change bet values, delete agroup of bits, or insert new bit values into a register.

> An typical application, register A is processor register and register B constitute togic operand extracted from memory & uplaced in reg B.

The selective set operation sets to 1 the bits in weg A where there \* Selective Set : are corresponding 1's in register B. At does not effect bit position that have

### e's in B.

yor example. 1010 -> A before  $| | 0 0 \rightarrow B (logic operand)$  $|| | 0 \rightarrow A$  after

4) The 2 leftmost bits of B are 1's, 30 the corresponding bits of A are set to 1 > The bits of A after the operation are obtained from the logic-OR operation of bits in B and preveous values of A.

\* Selective complement :-

The selective complement operation complements bits in A where there are selective clear corresponding is in B. At cloesnot affect bit positions that have o's in B

for example 1010 > d before  $1 1 0 0 \rightarrow B$  (logic Operand)  $0 \mid 10 \rightarrow A$  after

> The 2 leftmost bits of B are is, so the corresponding bits of A are complemented. The selective complement operation is just an X-OR microoperation. 7 \* relettive clear: The selective clear operation clears to 0 the bits in A only where the corresponding is in B. on example : Abelone 1010 Bllegic Operand) 1100 0010 A after . -> The leftmost bits of B one is, so the corresponding bits of A are cleaned to 0. -> The boolean operation performed on individual bits is AB. The corresponding logic microoperation is A ~ A AB. At is similar to selective clear except that the bits of A are \* Mask Operation : cleared only where there are corresponding o's in B. A before yon example, 1010 B (logic Operand) 1100 A (after masking) 1000 The 2 rightmost bits of A are cleared because the corresponding B bets are o's. The mask operation is an AND microoperation and it is more convenient than selective clean. \* Ansent :-Ansert operation inserts a new value into a graup of bits. This is done by first masking the bits and then ORing them with the veguired value. for example, suppose that an A vieguter contains 8 bits 0110 1010 To replace the 4 leftmost bits by value 1001 we first mask the four contraskes unwanted bits: dbefore 0110 1010 0000 1111 B(mask) A after masking 0000 1010

and the Insert new value

| 0000 | 1010 | A before          |

|------|------|-------------------|

| 1001 | 0000 | B (insert)        |

| 1001 | 1010 | A after insertion |

The mark operation is an AND microoperation & insert operation is an OR micro -operation.

\* Clean Operation :-

The clear operation compares the words in A and B and produces an all o's vesult if the two numbers are equal. This operation is achieved by an exclusive or micro-operation as shown by the following example:

$$\begin{array}{c} 1010 \\ 1010 \\ 8 \\ \hline 0000 \\ A \leftarrow A \textcircled{B} \\ \hline B \\ \hline \end{array}$$

when A&B are equal, the & corresponding bits are either both 0 on both 1. In either case the exclusive or operation produces a 0. The all-o's result is then checked to determine if the two numbers were equal.

## \* SHIFT MICROOPERATION 9 :-

Shift microoperations are used you serial transfer of data. They are also used in conjunction with withematic, logic and other data processing operations.

The contents of a register can be shifted to the left or the right. At the same time the bits are shifted, the first flip-flop receives its binary information from the serial input.

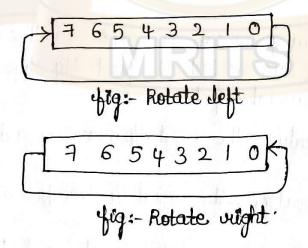

> During a shift left operation, the serial ip transfers a bit into the right -most position.

-> During a shift-night operation, the secial i/p transfers a bet into the left

most position. The information transferred through the serial input determines the type of shift. There are 3 types of shifts: logical, circular and arithematic

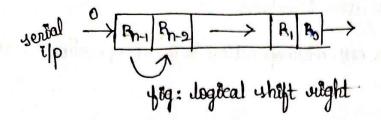

d logical shift is one that transfers O through serial i/p. We will adapt the symbols shland shr open logical shift left and shift night microoperations. -For example

RI + ShL RI R2← Shl R2 are 2 microoperations that specify a 1bit shift to left of the content of register R1 and a 1-bit shift to the right of the content of Register R2. The register symbol must be same on both sides of the arrow.

zig: logical shift left.

The lit transferred to the end position through the seried "/p is assumed to be 0 during a logical shift.

Circular shift circulates the lits of the register around the ends without loss of any information. In the case of logical shift, one of the end lits is lost.

Circular shift or rotate operation is performed by connecting the least significant bit to the teast most significant bit position. The symbolic representation is shown in fig

11. 14

we will use the symbols cil and cir for the circular shift left and night.

The symbolic notation for the shift microoperations is shown in below table

| symbolic designation | Descuption                         |

|----------------------|------------------------------------|

| symbolic anglitte    |                                    |

| R-shl R              | shift left vegister R              |

| R - sho R            | shift night negister R             |

| Rectir               | ctraular leftshift left register R |

| R <- clo R           | circular shift right register R    |

| Re-ashl R            | aveithematic shift left R          |

| ReashbR              | avithematic shift vight R          |

An duithematic shift is a microoperation that shifts a signed binary number to the left or sight. In drithematic shift left multiplies a signed binary number by 2. In drithematic shift right dévides the number by 2. drithematic shift right must leave the sign bit unchanged because the sign of the number remains same.

Jogieal shifts. Otherwise 2 shift operations are very similar.

The arithematic shift left és same as logic shift left ← Rn-1 Rn-9 ← R1 Rok-0 010->@

← Rn-1 Rn-2 ← R1 R0 ← O yig: drithematic shift left (ASL)

ASL inserts 0 into Ro & shifts all other bits to the left Anitial bit of Rn-1 is lost & replaced by the bit from Rn-2 & sign reversal occurs if B, Rn, changes in value after the shift. This happens if multiplication by 2 causes an overflow. Overflow occurs after an ASL if initially, before the shift Rn-1 + Rn-2

An overflow flipflop  $V_S$ , can be used to detect an ASL overflow  $V_S = R_{n-1} \bigoplus R_{n-2}$

Af Vs=0 there is no overflow, but if Vs=1 there is an overflow & a sign reversal after the shift. Vs must be transferred into overflow flipflop with the serve clackpulse that shifts the register

of possible choice for a shift unit would be a didentional shift \* Hardware Amplementation :-Arjonnation can be transferred to the register in parallel and then  $\rightarrow$ register with parallel load  $\rightarrow$ > In this type of configuration a clock pulse is needed for loading shifted to the night on left. the data into the negister and another pulse is needed to initiate An a processor unit with many registers it is more efficient to the shift implement the shift operations with a combinational circuit. > In this way the content of a register that has its be shifted in first placed onto a common bu whose of is connected to combinational shifter, & the shifted number is Then loaded back into the register At viequires only I clock julie for loading the stifted value into  $\rightarrow$ I combinational circuit shifter can be constructed with multiplexers the register. as shown in fig. below. The 4-bit shifter has 4 data i/p's, Ap to Az and 4 data o/p's, Ho to H3 select for shift right (down) sevial 1 bor shift left (up) input (IR) S IXG - Ho -Functiona Table MUX 0 select Output Ao Ho S  $H_1$   $H_2$ Hz S 2x1 H MUX 0 0 IR AO AI  $A_2$ 1 A2 A2 A3 1 A JL. A.3 S 2x1 MUX H2 0 I S axI -H3 MUY 0 Serial Input

> (I) Nog: 4-bit combinational const shifter

There are two serial i/ps, one for shift left (Iz) and other for shift suight (Iz). when the selection i/p s=0, the i/p data are shifted suight. when s=1, the i/p data are shifted left.

A shifter with n data E/p's & 0/p's vequires in multiplexers. The two seried E/p's can be controlled by another multiplexer to provide the 3 possible types of shifts.

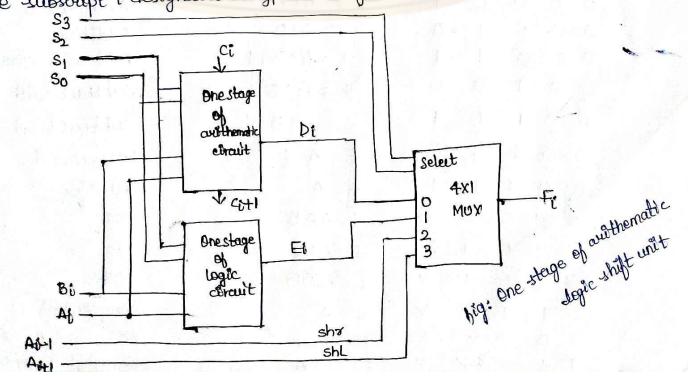

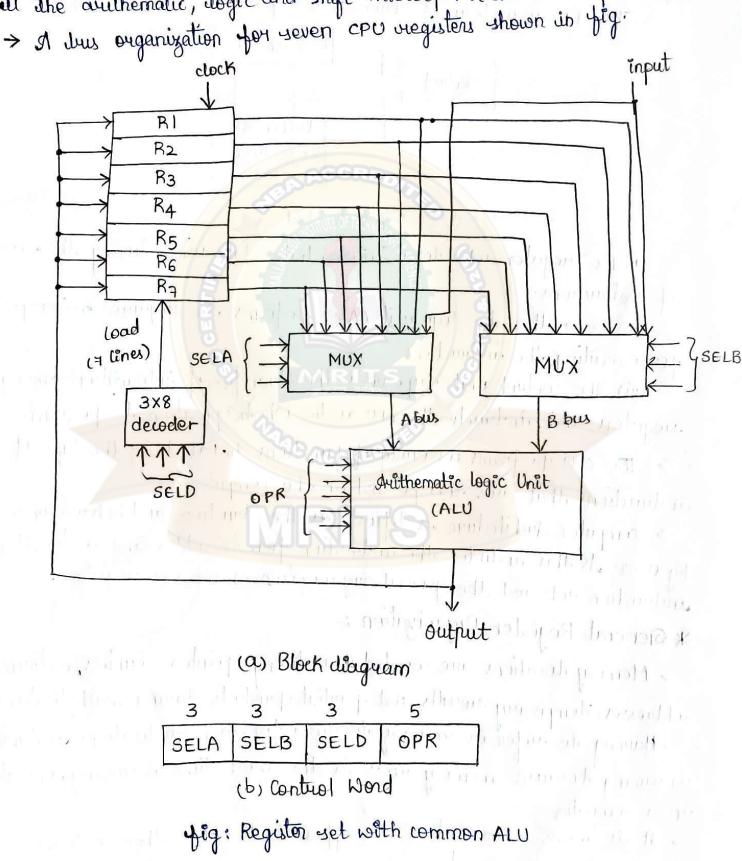

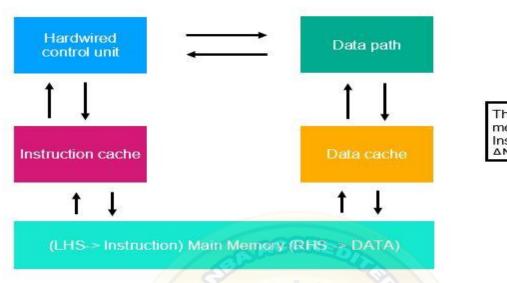

### \* ARITHMETIC LOGIC SHIFT UNIT:

→ Anstead of having individual registers performing the merooperations directly, computer rystems employ a number of storage registers connected to a common operational unit called an arithematic logic unit (ALU).

→ To perform a microoperation, the contents of specified registers are placed in the &p's of the common ALU.

> The ALL performs an operation & the verset is transforred to destination register.

> The ALV is a compensational ext so that the entire register transfer operation from the source registers through the ALV & ento the destination register can be performed during one clock pulse period.

→ The shift microoperations are efter performed in a seperate unit, but sometimes the shift unit is made part of the ALU.

→ The arithematic, logic and shift excusts introduced in can be combined into one ALU with common selection variables.

→ One stage of an Artthematic logic shift unit shown in below fig. The subswipt i designates a typical stage.

A Aparticular microspheriation is selected with the authematic & degic units.

A sparticular microspheriation is selected with the sign of the elp chooses blue an anithematic output Et and a degic of the H;

The data in the multiplexen are selected with the sign of the shiftThe other & data lips to the multiplexer vereive A<sub>i-1</sub> for the shiftThe cherit must be repeated in times for an m-bit ALU. The Output cavey C<sub>i+1</sub> of a given arithematic stage must be connected to the input cavey C<sub>i</sub> of mext stage in sequence. The collection variable for the authematic operation,

The clocuit provides eight cuithematic operation, your degic operation,

The clocuit provides eight cuithematic operation, your degic operation,

The clocuit provides eight cuithematic operation, your degic operation,

The clocuit provides eight cuithematic operation, your degic operation,

The clocuit provides eight cuithematic operation, your degic operation,

The clocuit provides eight cuithematic operation, your degic operation,

The clocuit of stage is selected with 5 variables s<sub>2</sub>, s<sub>2</sub>, s<sub>1</sub>, s<sub>0</sub> and c<sub>i</sub>n

The lip cavey con is used for selecting an arithematic operation only.

> The first 8 are arithematic quartiens and are selected with \$352=00.

→ The next 4 are logic """""""""""""  $S_3S_2 = 01$ → The ip carry has no effect during logic operations & marked as don't care x's.

→ The last 2 are shift operations and are selected with S352=10 and 11 → The other 3 selection i/ps have moeffect on shift.

| Operation select | GACCREDI      | Lysie in Sile - Sile |

|------------------|---------------|----------------------|

| S3 S2 S1 S0 Ctn  | Operation     | Function             |

| 00000            | F=A S         | Transfer A           |

| 00001            | F=At1         | Ancrement A          |

| 0 0 0 1 0        | F=A+B         | Addition             |

| 00011            | F = A + B + I | Add with carry       |

| 00100            | F=A+B         | subtract with barrow |

| 00101            | F= A+B+1      | subtraction          |

| 00110.           | F=A-1         | Decrement            |

| 00111            | ∓=A           | Transfer             |

| 0 1 0 0 X        | F=ANB .       | AND                  |

| 0 1 0 I X        | F=AVB         | OR                   |

| V I I O X        | F=A⊕B         | xor                  |

| 0 1 I I X        | F=A           | complement A         |

| I O X X X        | F=ShrA        | shift right A into F |

| 1 $X $ $X $ $X$  | F= ShLA       | shift left A Boto-F  |

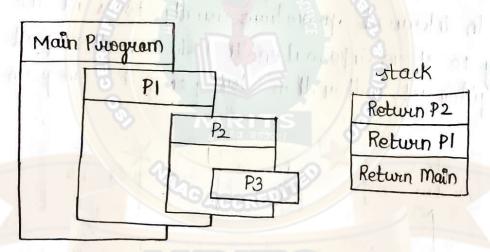

## Basic Computer Organization & design

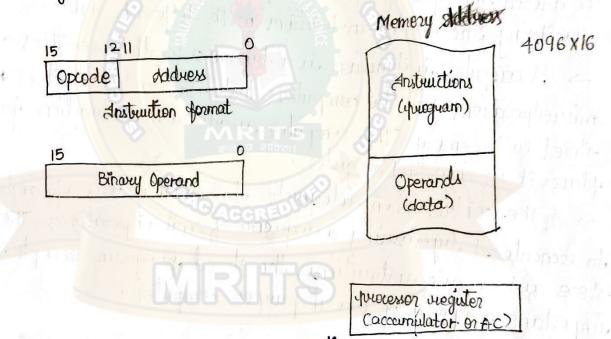

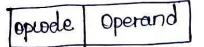

> The organization of the computer is defined by its internal registers Timing & control structures and the set of instructions it uses. → The internal organization of a digital system is defined by the sequence of microoperations it performs on data stored in its vegisters. -> The general purpose computer is capable of executing various mécrooperations & can be instructed as its what specific sequence of operations it must perform. The user of a computer can control the process -> I program is a set of instructions that specify the operations ground & the sequence by which processing has to occur. The dataprocessing task man be attered by specifying a new program with different instructions on spectfying the same instructions with different data. > A computer instruction is a binary code that specifies a sequence of microoperations for the computer. Anstruction code together with data are stored in memory. The computer reads each instruction from memory and -> The control then interprets the binary code of instruction & proceed to execute it by issuing a sequence of microoperations. The ability to store and execute instructions, the stored greegram concept is the most important property of general purpose computer. Anstruction Codes:-An instruction code is a group of lits that instruct the computer to perform a spécific operation. At is usually divided into parts, each having its own interpretation The most basic point of an instruction code is its operation point. The operation ade of an instruction is a group of bits that defines such operations as old, subtract, multiply, sheft & complement. > The no. of bits required for the operation code of an instruction depends on the total no of operations available in the computer→ The openation part of an instruction code specifies the operation to be performed. In instruction code must be there to specify not only the operation but also the registers & memory words.

Stored Russian Organization:

→ The simplest way to organize a computer is to have one process register and an instruction code format with two parts: Operation & studies.

→ The first part specifies the operation to be performed and second specifies an address.

→ The memory address tells the control where to yourd an operand in memory.

-> This operand is wead from memory and used as the data to be operated on together with the data stored in the processon wegister

au un

1 10 151

## , fig: stored priogram organization

→ Figure depicts this type of organization. Anstructions are stored in one section of memory and data in another. For a memory unit with 4096 words. we need 12 bits to specify an address since 2<sup>12</sup>=4096. Af we store each instruc -tion code in one 16-bit memory word, we have available four bits for the -tion code in one 16-bit memory word, we have available four bits for the operation code to specify one out of 16 possible operations and 12 bits to specify the address of an operand.

> The control reads a 16-bit instruction from the program portion of memory. At uses the 12-bit address part of the instruction to read a 16-bit operand from the data portion of memory. At then executes the operation specified by operation code, computers have a single processor register called decumulator (AC)

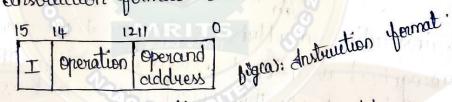

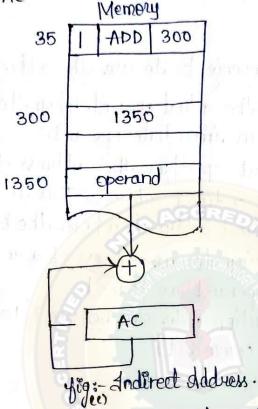

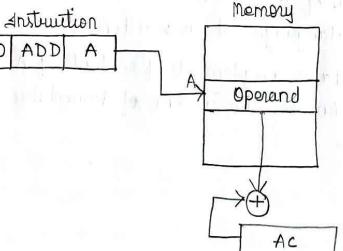

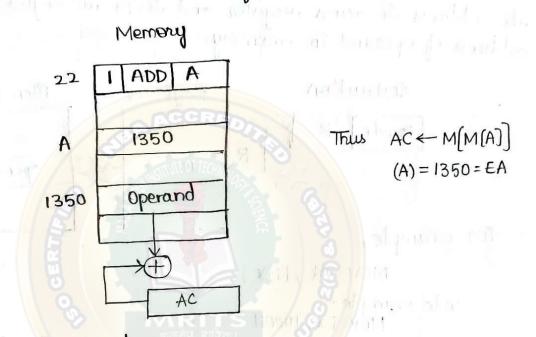

### Andirect Address:

At is sometimes convenient to use the address bet of an instruction code not as an address but the actual operand. When the second epart of an instruction is said to have an immediate operand.

when the second part specifies the address of an operand that unstruction is said to have a direct address. This is in contrast ito a third possibility called "Indirect address", where the bits in the second part of the instruction designate an address of a memory word in which the address of the operand is formed.

-> One wit of the instruction code can be used to distinguish between a direct & indirect address (MOD bit)

consider the instruction format as

At consists of 3 bit operation code, a la-bit address and a mode bit designated by I.

Tay mod bit is 0 you => direct address

⇒ Andirect address. ap mod bit is 1

I direct address instruction is shown in fig.

-> Is it is placed in address 22 in memory. The I bit is 0, so the instruction is recognized as a direct address instruction. The Opende specifies an ADD instruction & address part is the simary equivalent of 457. The control finds the operand in memory at address 457 and adds it to the content of AC.

Weil W. Letter J. and W.

which all handles

> The instruction in address 35 shown in fig has a mode bit I=1. Therefore it is recognized as indirect address instruction. The address part is the binary equivalent of 300. The control goes to address 300 to find the address of the operand. -> The address of the operand in this case is 1350. The operand found in

address 1350 is then added to the content of AC.

-> The indirect Address instruction needs 2 references to memory to yetch an operand. The first reference is needed to read the address of the operand, the second is for the operand itself.

# Effective address:-

The address of the operand in computation type instruction or the target address in a branch type instruction

The effective address in instruction of yEg(b) is 457 & the instruction of fig (6) is 1350.

· module faster -1

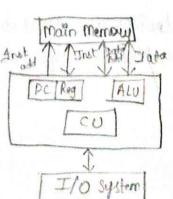

\* Computer Registers :-

→ Computer instructions are normally stored in consecutive memory Jocations and are executed sequentially one at a time

→ The control reads an instruction from a specific address in memory and executes it. At then continues by reading the next instruction in sequence & executes it & soon.

→ This type of instruction sequencing needs a counter to calculate the address of the next instruction after execution of the current instruction is completed.

→ At is also necessary to provide a register in the control unit for storing the instruction code after it is read from memory.

→ The computer needs proversor register for manipulates data and a

→ The computer needs proversor register for manipulates data and a

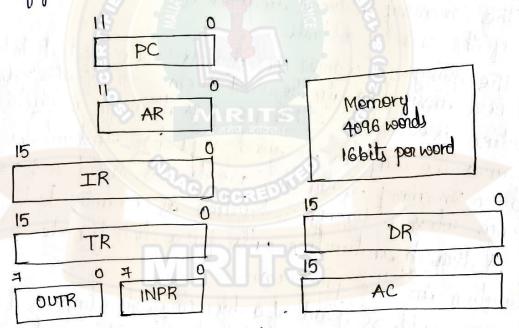

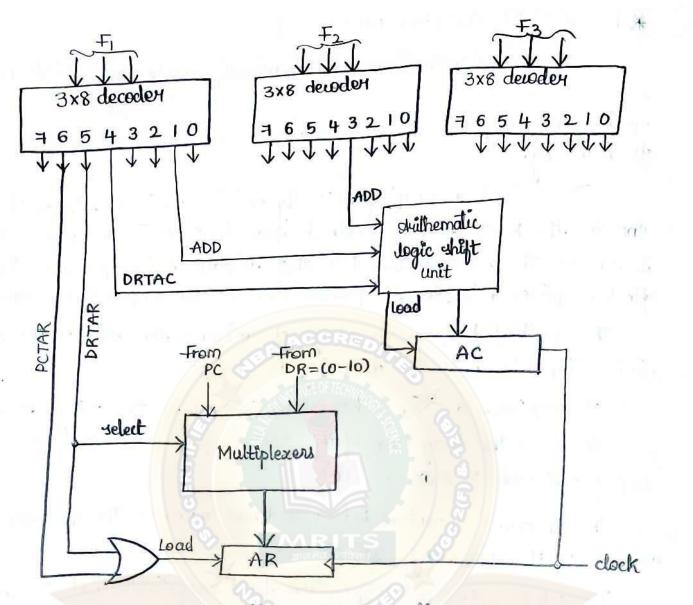

wegister for holding a memory address. These requirements dicatetethe register configuration shown in below fig

fig :- Baste computer registers and memory

| Table:<br>Register Symbol | No-of bits | Register Name                     | -Function<br>Holds memory operand |

|---------------------------|------------|-----------------------------------|-----------------------------------|

| DR                        | 16         | Data Register<br>Address register | Holds address for memory          |

| AR<br>AC                  | 12<br>16   | Accumulator                       | Purocesson registers              |

| IR ·                      | 16         | Anstruction register              | Holds instruction code            |

| PC                        | 10         | Ruguam Counter                    | Holds address of instruction      |

| TR                        | 16         | Temporary register                | Holds temporary data              |

| INPR                      | 8          | annut register                    | Holds Annut character             |

| OUTR                      | 8          | output register                   | Holds Output character            |

> The negister are listed in the table together with a brief description of their junction and the number of bits that they contain. > The memory whit has a capacity of 4096 words and each word contains 16 bits. 12 bits of an instruction word are needed to specify > This leaves 3 bits for the operation part of the instruction and a bit to specify a direct or indirect address.

4) The data register (DR) holds the operand read from memory. 4) The Accumulator (AC) register is a general purpose processing

4) The instruction read from memory is placed in instruction register register

SThe temporary register (TR) is used for holding temporary data (IR.).

The memory address register (AR) has 12 bits since this is the during the processing.

of the next instruction to be read from memory after the current width of the memory address. instruction is executed. The PC goes through a courting sequence and causes the computer to read sequential instructions previously stored in memory instruction words are read and executed in sequence unless a branch instruction is encountered. > A branch instruction calls for a transfer ito a nonconsecutive

instruction in the program. > The address part of a branch instruction is transferred to PC to become the address of next instruction. To read an instruction, to become une number as the address for memory & a memory the content of PC is taken as the address for memory & a memory the content of PC is invienented by one, So it holds the need eyele is initiated. PC is invienented by one, So it holds the address of the next instruction in sequence. > Two registers are used for input and output. The input register UNPR) neretves an 8-bit cheviater from an input device. The output register LOUTR) holds an 8-bit character for an output

device.

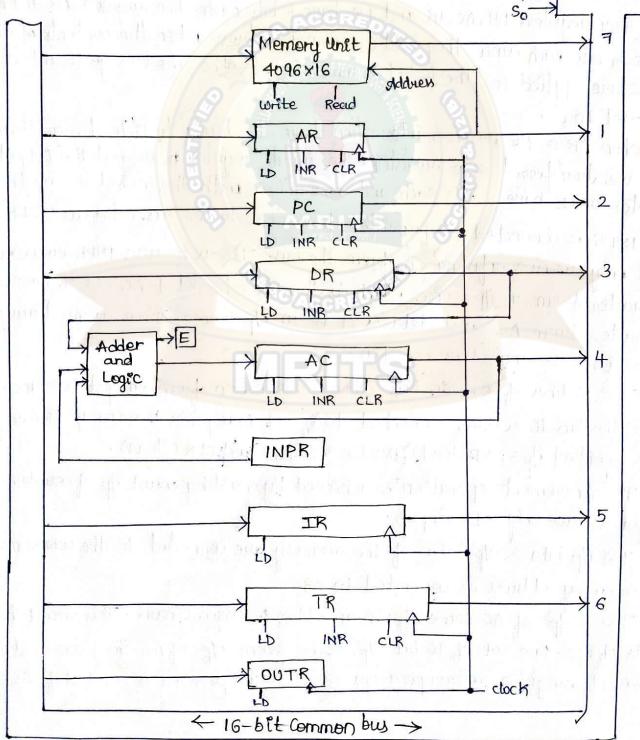

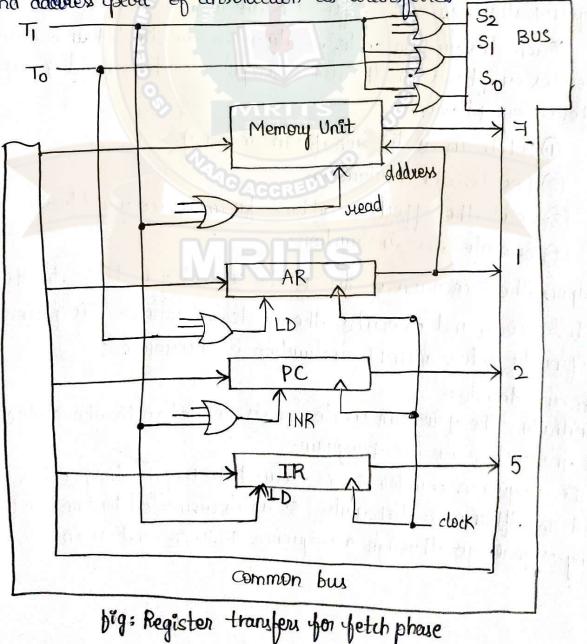

\* Common Jus system:

The basic computer has 8 registers, a memory unit and a control unit. Paths must be provided to transfer information from one register to another and between memory and registers.

The number of wires will be excessive if connections are made b/w the o/p's of each register & the i/p's of other registers. So a more efficient scheme is a common trus system which is employed in 4-bit common trus system using multiplexes & three-state buffers.

The connection of registers & memory of the baric computer to a common bus system is shown in fig. The outputs of 7 registers & memory are connected to the common bus.

The specific of that is selected for the bus lines at any given time is determined from the binary value of the selection variable 5, 5, and 50.

The number along each of shows the decimal equivalent of the required binary selection. For example, the number along the output of DR is 3.

The 16-bit o/p's of DR are placed on the bus lines when S25, S0=011.

Since the binary value of decimal 3.  $\rightarrow$  The lines of from the common bus are connected to the ip's of each register and the data ip's of memory. The particular register whose LD(load) ip is enabled receives the data from the bus during the mext clock pulse transition.  $\rightarrow$  The memory receives the contents of the bus roher its write i/p is activated. The memory receives its 16-bit Outputs onto the drus when the #p read i/p is attivated and  $s_{s}s_{1}s_{0}=111$ .

→ Four registers DR, AC, IR and TR, have 16 bits each. Two registers AR and PC, have 12 bits each since they hold a memory address. when the contents of AR have 12 bits each since they hold a memory address. when the contents of AR have 12 bits each since they hold a memory address. when the contents of AR have 12 bits each since they hold a memory address. when the contents of AR have 12 bits each since they hold a memory address. when the contents of AR have 12 bits each since they hold a memory address. when the contents of AR have 12 bits each since they hold a memory address. When the contents of AR have 12 bits each since they hold a memory address. When the contents of AR have 12 bits each since they hold a memory address. When the contents of AR

ave set to 05. > when AR on PC weceive information from the bus, only 12 deast significant bit are transferred into register. The input register INPR and the Output bit are transferred into register. The input register INPR and the Output register OUTR have 8 bits each and communicate with the \$8 LSB's in the bus register OUTR have 8 bits each and communicate with the bus. whereas OUTR ear > INPR is connected to growide information to the bus. whereas OUTR ear isin only receive information from the bus. This is because INPR receives a character from an ip device which is then transferred to AC. OUTR receives a character from Ac and delivers it to an op device. There is no transfer prom outre to any other registers.

→ The 16 lines of common bus receive information from 6 registers & memory unit. The bus lines are connected to ips of 6 registers & memory. Five register have 3 control ip's: LD(load), INR tincrement) and CLR ( clean).

-> The invienment operation is achieved by enabling count ip of counter. 2 viegisters have only a LD input.

> The ipdata & opdata of the memory are connected to the common bus but memory address is connected to AR.

→ The 16 ilp's of AC come from an adder & logic circuit. This circuit has 3 sets of ilp's. One set of 16-bit ilp's come from olp's of AC. They are used to implement vegister microoperations such as complement AC and shift AC. → Shother set of 16-bit inputs come from an the DR. The i/ps from DR to AC are used for drithematic & logic microoperations, such as add DR to AC on AND DR to AC. The result of addition is transferred to AC and end carry-out of the addition is transferred to flip flop E.

→ A third set of 8-bit 1/p's come from input register INPR.

For example :- Consider two micro operations

### DR - AC and AC DR

→ The two microoperations can be executed at the same time. This can be done by placing the content of AC on the bus, enabling the LD i/p of DR, transferring the content of DR through adder & logic circuit into AC and enabling the LD (load) i/p of AC, all during same clock cycle.

→ The 2 transfers occurs upon the arrival of the clock pulse transition

→ The 2 transfers occur upon the arrival of the clock pulse transition at the end of the clock cycle.

## \* Computer Anstructions:-

The basic computer has three instruction code formats shown in fig. Each format has 16 bits.

The operation code (opcode) part of the instruction contains three bits and the meaning of the remaining 13 bits depends on the operation code encountered

15 14 1211

$$I$$

Opticle Address (opticle = 000 through 110)

(a) Memory-vieference instruction

15 1211 0

(a) Memory-vieference instruction

15 1211 0

(b) Register-vieference instruction

15 1211 0

(b) Register-vieference instruction

15 1211 0

(b) Register-vieference instruction

(b) Register-vieference instruction

(c) Anput - Output instruction

Sa: Basic. Commiter instruction format.

I memory-reference instruction uses 12 bits to specify an address and one wit to specify an address and one bit to specify the addressing mode 2.

⇒ I us equal to 0 for direct address

I=1 you indirect address.

> The register reference instructions are recognized by the operation code 111 with a 0 in leftmost bit (bit 15) of the instruction. I register reference instruction specifies an operation on or a dest of the AC register. An operand from memory is not needed; therefore, the other 12 bits are used to specify the operation or test to be executed

> In Annut-Dutput instruction does not need a reference to memory and is viecegnized by the operation code III with a I in the leftmost bit of the instruction. The memaining 12 bits are used to specify the type of input Output operation or test performed

> The type of instruction is recognized by the computer control from the 4 bits in positions 12 through 15 of the instruction. If the 3 grade bits in positions 12 through 14 are not equal to 111, the Bit is your instruction is a memory-reference type and the bit in position 15 is taken as the addressing mode I

> Af 3 bit Opcode is equal to 111, control then inspects the bit in position A bit=0 then register reference itype 15. bit=1 then Annut-Output type?

Only 3 bits of instruction are used for the opende. At seems that the  $\rightarrow$ computer is reslucted to maximum of eight distint operations.

> However, since register-reference and input-output instructions use the remaining 12 bits as part of operation code, the total no of instruction can exceed eight

> An fact, the total number of instructions chosen for the basic computer is equal to 25.

> The instructions for the computer are disted in Table. The symbol designation is a three-letter word and represents an abbreviation intended for programmers & users. The hexadecimal code is equal to the equivalent hexadecismal number of the binary code used for the instruction of the an low could ar play of 10,

By using the hexadecimal equivalent we reduce the 16 bits of an instruction code to 4 digits with each hexadecimal digit being equivalent to 4 bits.

Memory reference Anstructions:

| 3911,001                                      | Heradecimal Code                                                          |                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               | <u>I=0</u>                                                                | <u> </u>                                     | AND memory word to AC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AND<br>ADD<br>LDA<br>STA<br>BUN<br>BSA<br>NSZ | 0 x x x<br>1 x x x<br>2 x x x<br>3 x x x<br>4 x x x<br>5 x x x<br>6 x x x | 8×××<br>9×××<br>A×××<br>B×××<br>D×××<br>E××X | AND memory word to AC<br>Add memory word to AC<br>Load memory word to AC<br>Store content of AC &n<br>memory<br>Branch chiconditionally<br>Branch & save return address<br>Increment and ship if zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                               |                                                                           | - Anife                                      | ACT CONTRACTOR OF THE OWNER OWNER OF THE OWNER OWNE |

Register reference instructions :-

| Symbol | Hessadecimal Code | Description                          |

|--------|-------------------|--------------------------------------|

| CLA    | 7800              | clear AC                             |

| CLE    | 7400              | clear E                              |

| CMA    | 7200 ACCRED       | complement AC                        |

| CME    | 7100              | complement E                         |

| ÇIR    | 7080              | circulate sight AC and E             |

| CIL    | 7040              | circulate left AC and E              |

| INC    | 9020              | Increment AC                         |

| SPA    | 7010              | skip next instruction if AC positive |

| SNA    | 7008              | shop next instruction if Ac negative |

| SZA    | 7004              | ship next instruction If Ac zero     |

| SZE    | 7002              | skip next Enstruction if EisO        |

| HLT    | 7001              | Halt computer                        |

|        |                   |                                      |

Matalitan Water to but the

Input-Output instruction:-

| Symbol | Hexadecimal code   | Description              |

|--------|--------------------|--------------------------|

| INP    | <del>1</del> 800   | Annut character to AC    |

| OUT    | F400 111           | Output character from AC |

| ski    | F200 1             | skep on input flag       |

| SKO    | F100               | skip on output flag      |

| ION    | . <del>4</del> 080 | Anterrupt on             |

| 10F    | F040               | Interrupt Off            |

A memory reference instruction has an address part of 12 bits. The address part is denoted by three X's and stand for the three hexadecimal digits corresponding to the 12-bit Address.

The last bit of instruction is designated by I

when I=0, the last 4 bits of an instruction have a hexaderismal digit equivalent from 0 to 6 since the last bit is 0.

of the instruction varges from 8 to E since the last bit is 1.

\* Anstruction Set completenes:-

→ d'computer should have a set of instructions so that the user can construct machine language programs to evaluate any function that is known to be computable.

→ The set of instructions are said to be complete if the complete computer includes a sufficient number of instructions in each of the fellowing categories

() duithematic, logical and shift instructions.

2 Anstructions for moving information to and from memory and process -or registers.

3 Riogram Control instruction together with instructions that check

(4) Annut and Output instructions.

> suithematic, legical and shift instructions provide computational capabilities for processing the type of data that the user may wish to employ.

The welk of the binary information in a digital computer is stored in memory, but all computations are done in processor registers. So, the user must have the capability of moving information between these two units.

Program control instructions such as branch instructions are used to change the sequence in which the program is executed.

Annut and Output instructions are needed for communication between the computer & usen.

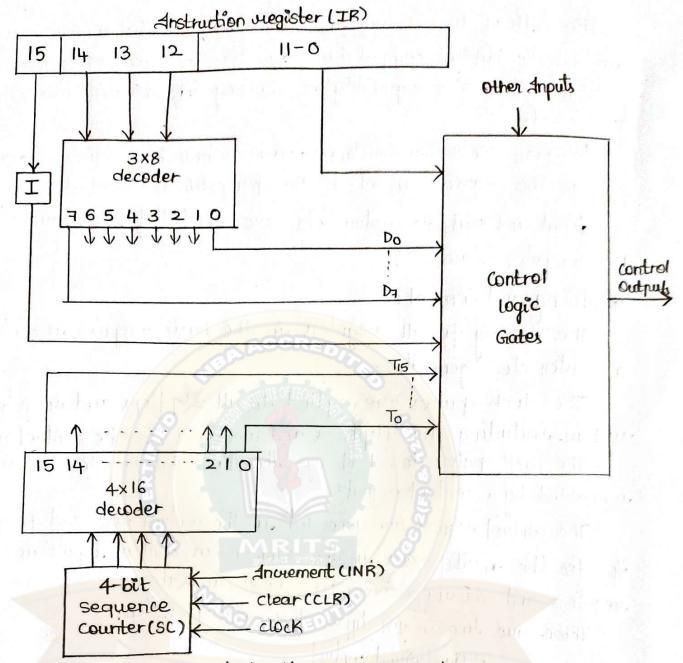

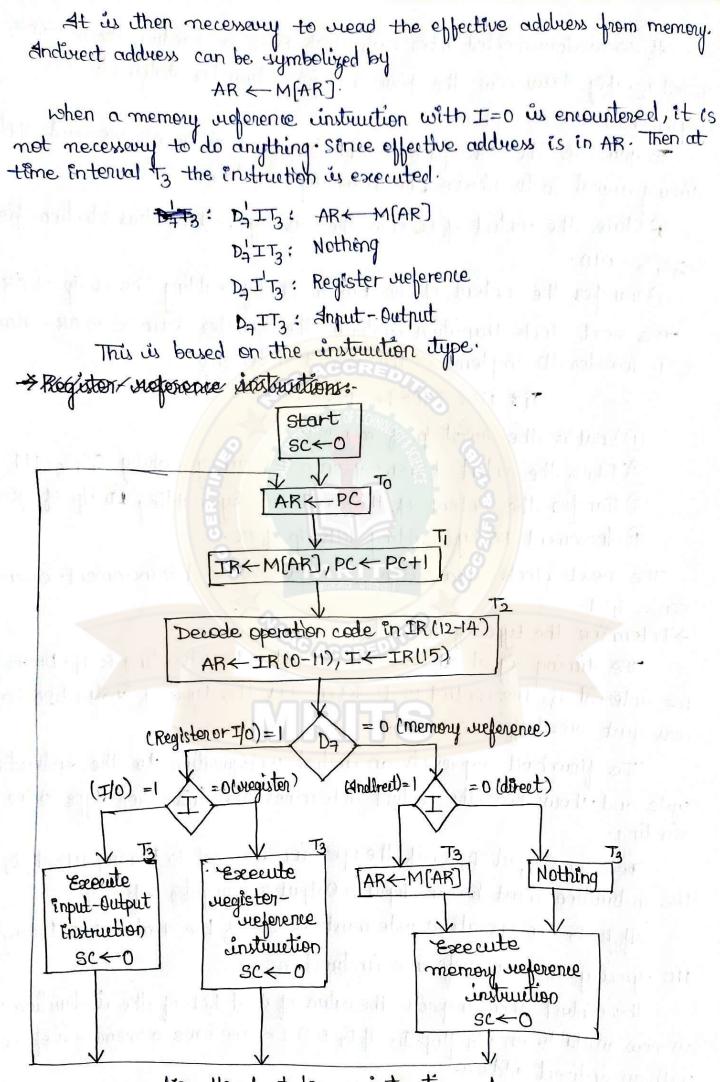

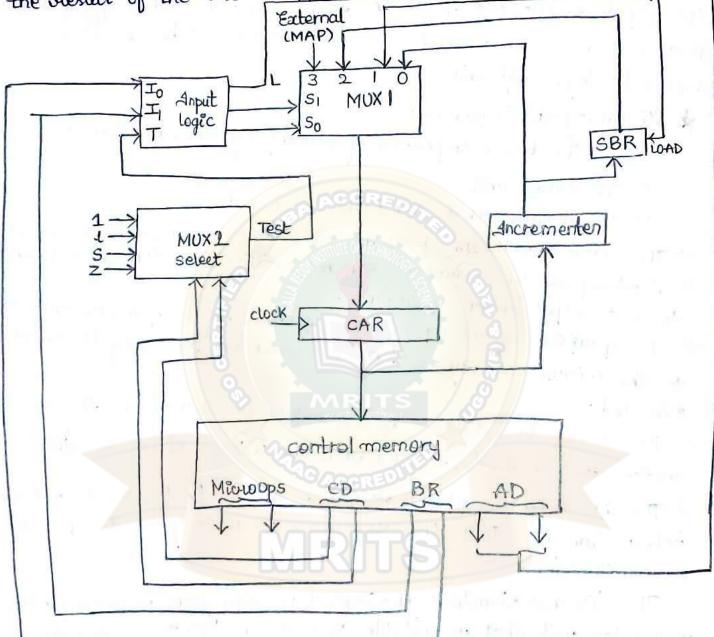

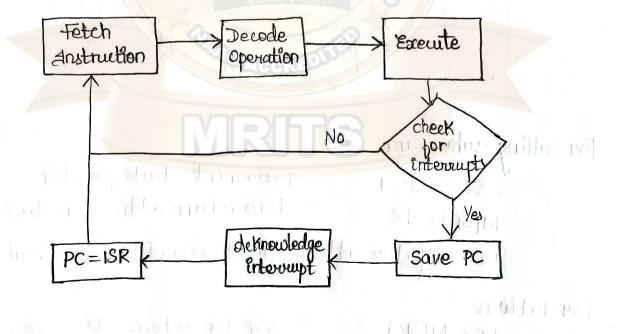

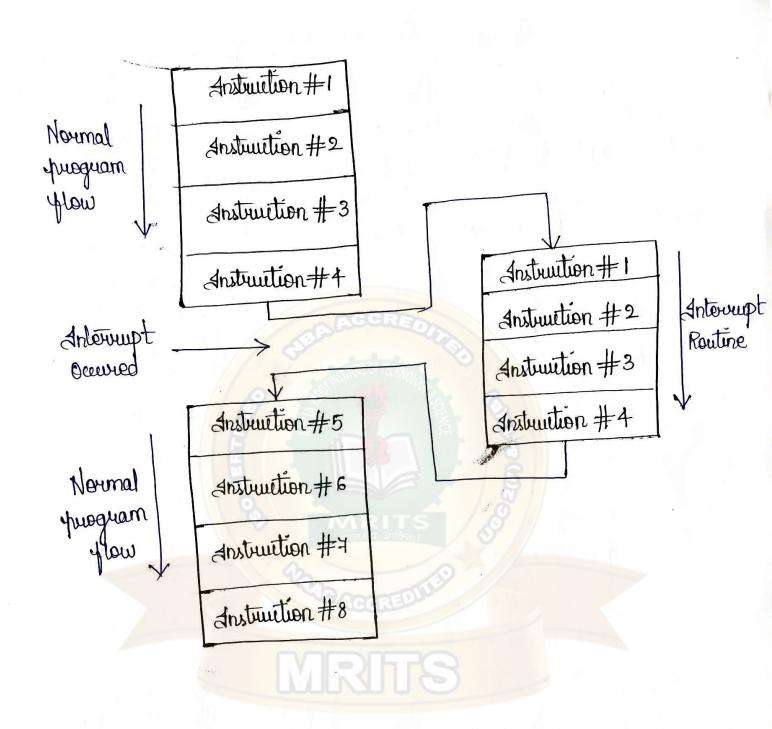

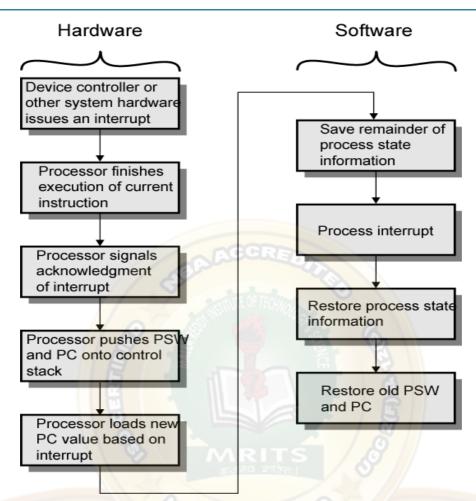

\* Timing and Control:-

The timing for all registers in the basic computer is controlled by a master clock generator.

The clock pulses are applied to all flipplops and registers in the system, including the flipplops and vegisters in the control unit.

The clock milses do not change the state of a register unless the register is enabled by a control signal.

The control signals are generated in the control unit and provide control Ip's yer the multiplexers in the common bus, control inputs in processor registers and microoperations for the accumulator.

There are two major types of control organization:

() Hardwired control

(2) Microprogrammed control.

An hardwired organization, the control Logic is implemented with gates, flipflops, decoders and other digital circuits At has advantage that it can be optimized to produce a just mode of operation.

An microprogrammed organization, the control information is stored in a control memory. The control memory is programmed to initiate the required sequence of microoperations.

A hardwired control as the name implies, requires changes in the wiring among the various components if the design has to be modified or changed. An the microprogrammed control, any required changes or modifications can be dene by updating the microprogram in central memory.

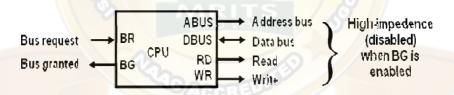

fig: Control unit of basic computer

→ The block diagram of the control wit is shown in fig. At consists of two decoders, a sequence counter and a number of control dogic gates. An instruction read from memory is placed in the instruction register (IR).

> The operation code in Lits 12 through 14 are decoded with a 3x8 decodor The eight outputs of the decoder are designated by symbols Do through D7. The subsvipted decimal number is equivalent to the binary value of the corresponding operation code. Bit 15 of the instruction is transferenced to a flipplop designated by the symbol I.

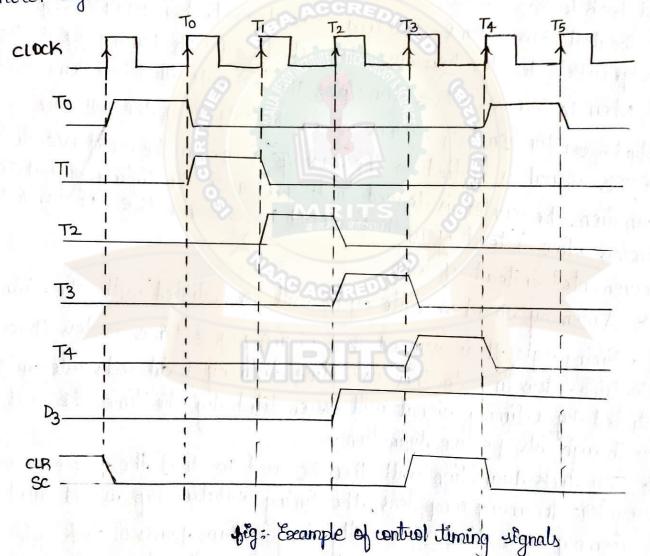

→ Bits 0 through 11 are applied to the control logic gates. The 4-bit sequence counter can count in binary from 0 through 15. The Output of counter are decoded into 16 timing signals To through T15. The sequence counter sc can be invemented or cleaved synchronously.

Most of the time, the counter is incremented to provide the sequence of timing signals out of the 4x16 decoder. Once in awhile, the counter is cleared to 0, causing the next active timing signal to be TO.

For example, consider the case where SC is incremented to provide timing signals TO, TI, T2, T3, T4 in sequence. At time T4, SC is cleared to 0, if decoder output D3 is active. This is symbolically expressed as

D3T4:5C←0

The timing diagram of figure shows the time velationship of the control signals.

to a station of purson in the sold

and by to mid the bit.

and the state of t

Sector D. A. Chapterio

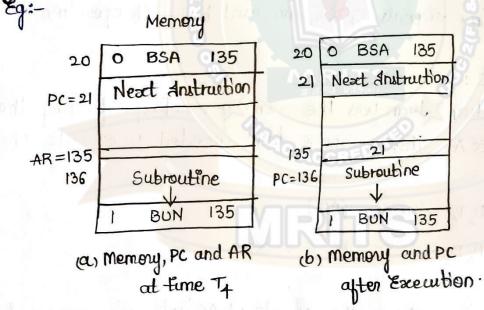

to de la ligo do parte